# **Introduction to Microdisplays**

## **Wiley-SID Series in Display Technology**

Series Editor:

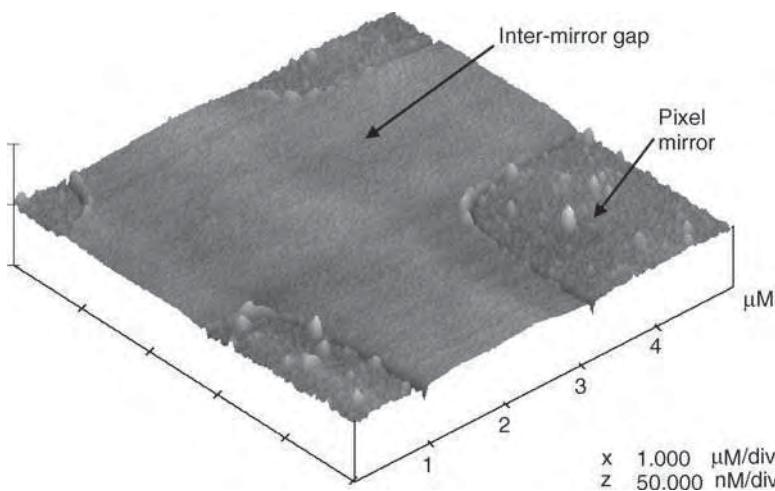

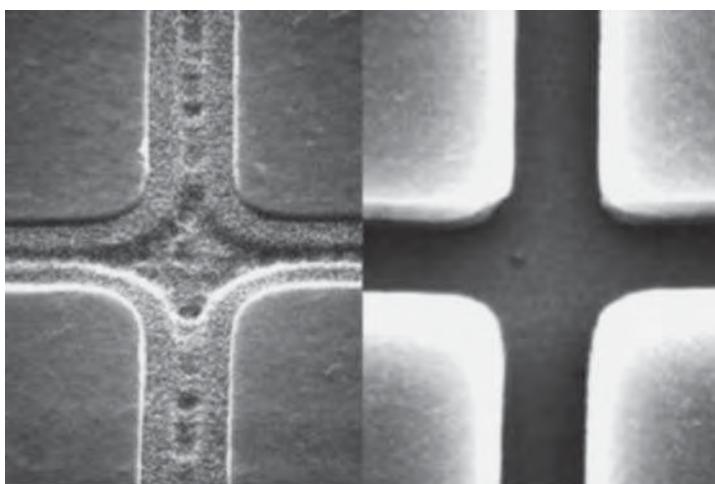

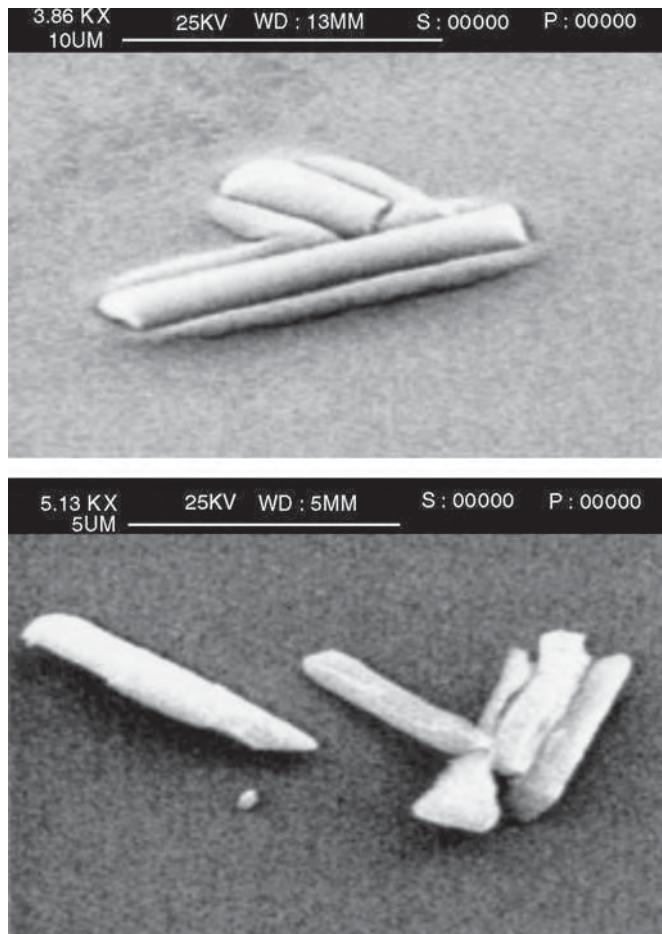

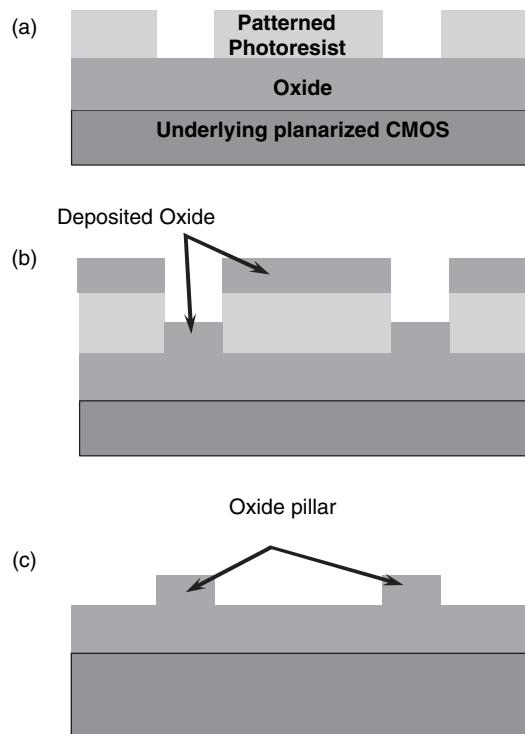

**Anthony C. Lowe**

Consultant Editor:

**Michael A. Kriss**

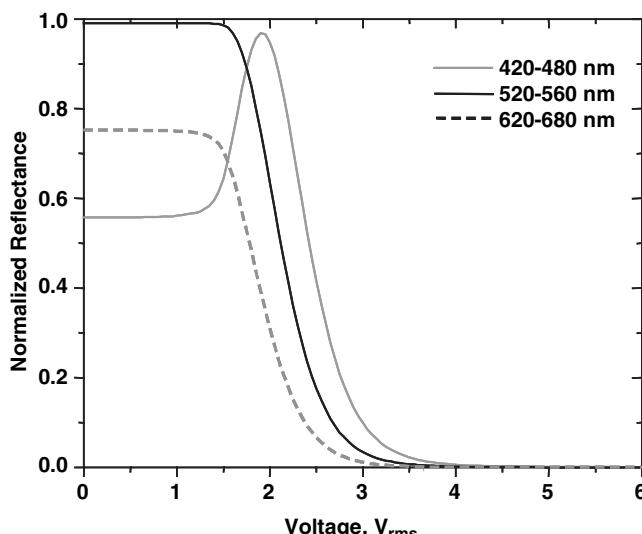

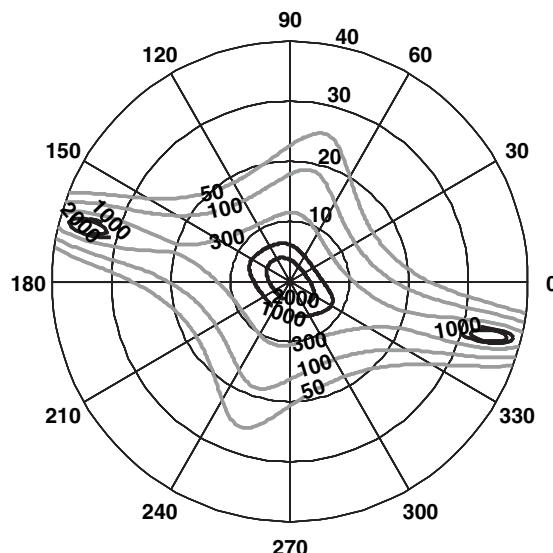

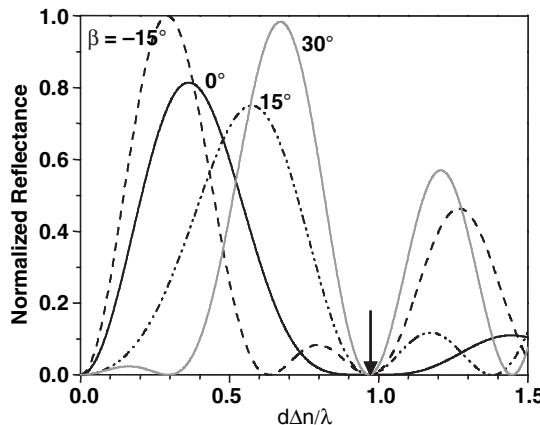

---

Display Systems:

Design and Applications

**Lindsay W. Macdonald and Anthony C. Lowe (Eds)**

Electronic Display Measurement:

Concepts, Techniques and Instrumentation

**Peter A. Keller**

Projection Displays

**Edward H. Stupp and Matthew S. Brennesholz**

Liquid Crystal Displays:

Addressing Schemes and Electro-Optical Effects

**Ernst Lueder**

Reflective Liquid Crystal Displays

**Shin-Tson Wu and Deng-Ke Yang**

Colour Engineering:

Achieving Device Independent Colour

**Phil Green and Lindsay MacDonald (Eds)**

Display Interfaces:

Fundamentals and Standards

**Robert L. Myers**

Digital Image Display:

Algorithms and Implementation

**Gheorghe Berbecel**

Flexible Flat Panel Displays

**Gregory Crawford (Ed.)**

Polarization Engineering for LCD Projection

**Michel G. Robinson, Jianmin Chen, and Gary D. Sharp**

Fundamentals of Liquid Crystal Devices

**Deng-Ke Yang and Shin-Tson Wu**

Introduction to Microdisplays

**David Armitage, Ian Underwood and Shin-Tson Wu**

# Introduction to Microdisplays

---

**David Armitage**

*Consultant, Los Altos, California, USA*

**Ian Underwood**

*MicroEmissive Displays Ltd, Edinburgh, UK*

**Shin-Tson Wu**

*University of Central Florida, Florida, USA*

John Wiley & Sons, Ltd

Copyright © 2006

John Wiley & Sons Ltd, The Atrium, Southern Gate, Chichester,

West Sussex PO19 8SQ, England

Telephone (+44) 1243 779777

Email (for orders and customer service enquiries): [cs-books@wiley.co.uk](mailto:cs-books@wiley.co.uk)

Visit our Home Page on [www.wiley.com](http://www.wiley.com)

All Rights Reserved. No part of this publication may be reproduced, stored in a retrieval system or transmitted in any form or by any means, electronic, mechanical, photocopying, recording, scanning or otherwise, except under the terms of the Copyright, Designs and Patents Act 1988 or under the terms of a licence issued by the Copyright Licensing Agency Ltd, 90 Tottenham Court Road, London W1T 4LP, UK, without the permission in writing of the Publisher. Requests to the Publisher should be addressed to the Permissions Department, John Wiley & Sons Ltd, The Atrium, Southern Gate, Chichester, West Sussex PO19 8SQ, England, or emailed to [permreq@wiley.co.uk](mailto:permreq@wiley.co.uk), or faxed to (+44) 1243 770620.

Designations used by companies to distinguish their products are often claimed as trademarks. All brand names and product names used in this book are trade names, service marks, trademarks or registered trademarks of their respective owners. The Publisher is not associated with any product or vendor mentioned in this book.

This publication is designed to provide accurate and authoritative information in regard to the subject matter covered. It is sold on the understanding that the Publisher is not engaged in rendering professional services. If professional advice or other expert assistance is required, the services of a competent professional should be sought.

#### ***Other Wiley Editorial Offices***

John Wiley & Sons Inc., 111 River Street, Hoboken, NJ 07030, USA

Jossey-Bass, 989 Market Street, San Francisco, CA 94103-1741, USA

Wiley-VCH Verlag GmbH, Boschstr. 12, D-69469 Weinheim, Germany

John Wiley & Sons Australia Ltd, 42 McDougall Street, Milton, Queensland 4064, Australia

John Wiley & Sons (Asia) Pte Ltd, 2 Clementi Loop #02-01, Jin Xing Distripark, Singapore 129809

John Wiley & Sons Canada Ltd, 6045 Freemont Blvd, Mississauga, ONT, L5R 4J3

Wiley also publishes its books in a variety of electronic formats. Some content that appears in print may not be available in electronic books.

#### ***British Library Cataloguing in Publication Data***

A catalogue record for this book is available from the British Library

ISBN-13 978-0-470-85281-1 (HB)

ISBN-10 0-470-85281-X (HB)

Typeset in 9/11 pt Times by Thomson Digital

Printed and bound in Great Britain by Antony Rowe Ltd, Chippenham, Wiltshire

This book is printed on acid-free paper responsibly manufactured from sustainable forestry

in which at least two trees are planted for each one used for paper production.

# Contents

---

|                                      |             |

|--------------------------------------|-------------|

| <b>Series Editor's Foreword</b>      | <b>xiii</b> |

| <b>Preface</b>                       | <b>xv</b>   |

| <b>1. Introduction</b>               | <b>1</b>    |

| 1.1 Microdisplays                    | 1           |

| 1.2 Human Factors                    | 3           |

| 1.2.1 Color                          | 4           |

| 1.2.2 Resolution                     | 4           |

| 1.2.3 Flicker                        | 5           |

| 1.2.4 Contrast Ratio                 | 6           |

| 1.2.5 Grayscale                      | 7           |

| 1.2.6 Viewing Comfort                | 7           |

| 1.3 Display Specifications           | 8           |

| 1.3.1 Resolution and Size            | 8           |

| 1.3.2 Luminance and Color Saturation | 8           |

| 1.3.3 Contrast Ratio and Grayscale   | 9           |

| 1.3.4 Response Speed and Flicker     | 9           |

| 1.4 Displays in General              | 10          |

| 1.4.1 Cathode Ray Tube               | 10          |

| 1.4.2 Matrix Addressed Displays      | 10          |

| 1.4.3 Field Emission Displays        | 11          |

| 1.4.4 Plasma Displays                | 11          |

| 1.4.5 Liquid Crystal Displays        | 12          |

| 1.4.6 Electroluminescent Displays    | 12          |

| 1.4.7 Electromechanical Displays     | 12          |

| 1.5 Microdisplay Evolution           | 13          |

| 1.6 Microdisplay Applications        | 15          |

| 1.6.1 Projection Displays            | 15          |

| 1.6.2 Near-to-Eye Displays           | 15          |

| 1.6.3 Other Applications             | 16          |

| 1.7 References                       | 17          |

|                                                                   |           |

|-------------------------------------------------------------------|-----------|

| <b>2. Electronic Addressing</b>                                   | <b>19</b> |

| 2.1 Introduction                                                  | 19        |

| 2.1.1 General Introduction                                        | 19        |

| 2.1.2 Addressing Methods                                          | 19        |

| 2.1.3 Grayscale                                                   | 23        |

| 2.1.4 Color                                                       | 25        |

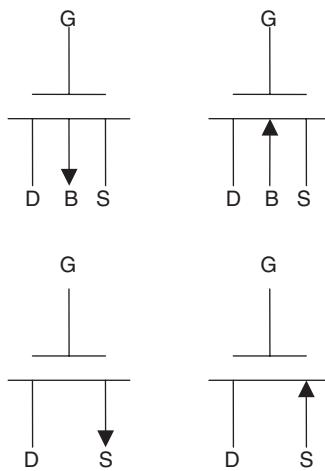

| 2.1.5 Active Matrix Technologies                                  | 28        |

| 2.1.6 LCOS: The Early Days                                        | 30        |

| 2.2 The MOS Transistor                                            | 32        |

| 2.2.1 Characteristic Equations                                    | 32        |

| 2.2.2 MOS Capacitor                                               | 37        |

| 2.2.3 MOS Transistor Switches                                     | 37        |

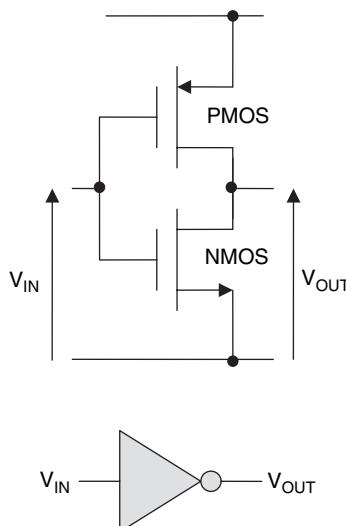

| 2.2.4 CMOS Inverter                                               | 38        |

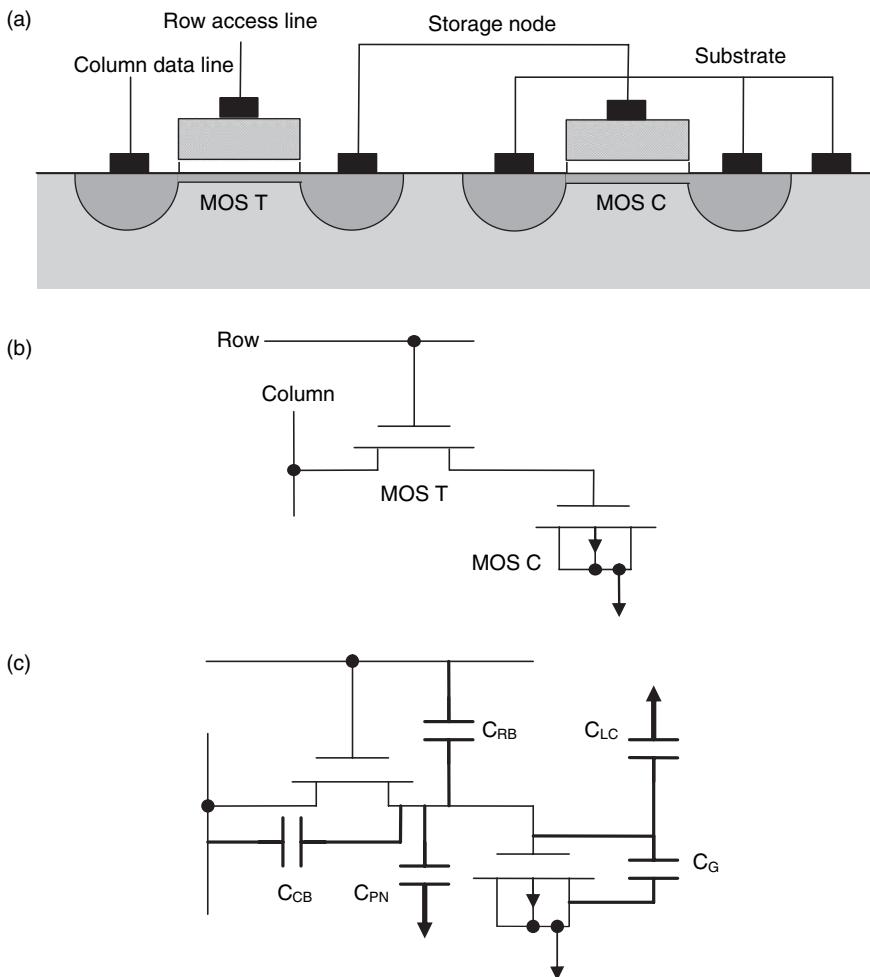

| 2.2.5 MOS Memory Circuits                                         | 39        |

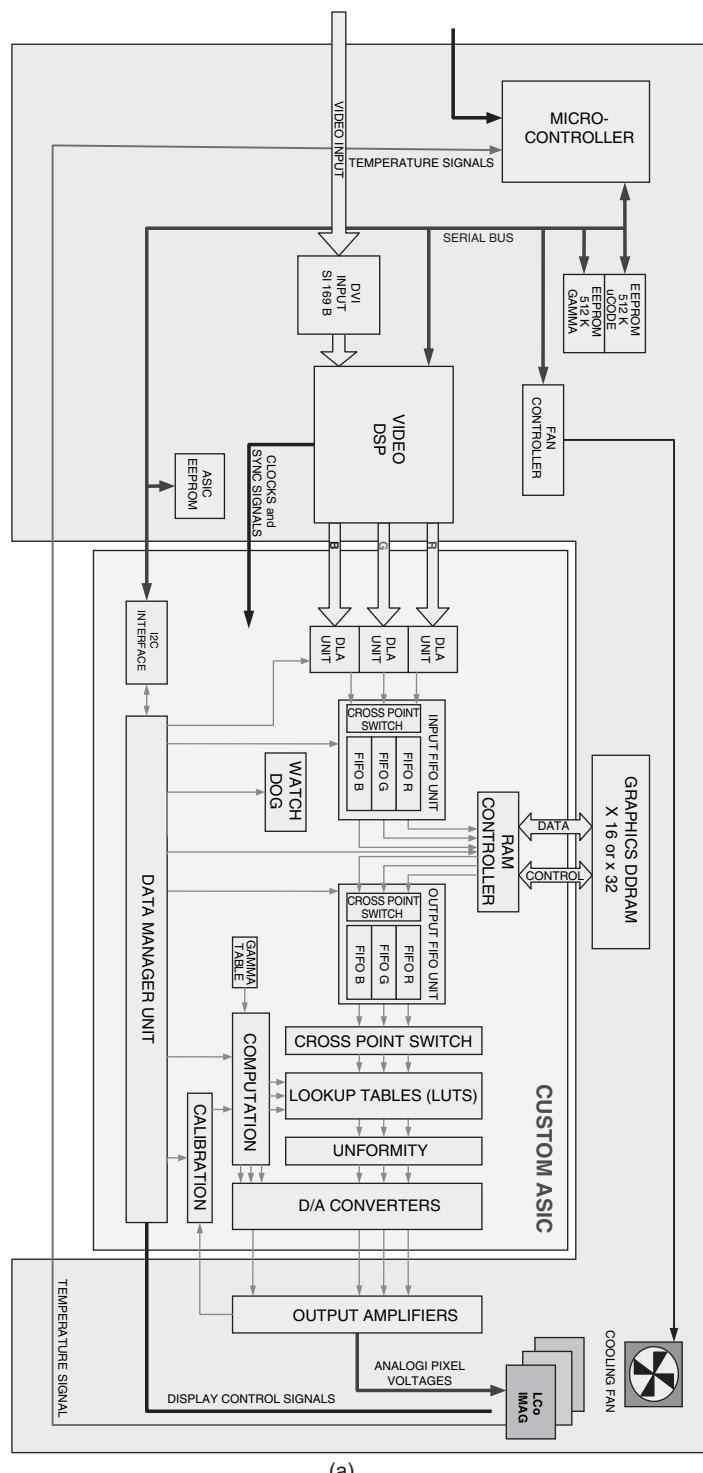

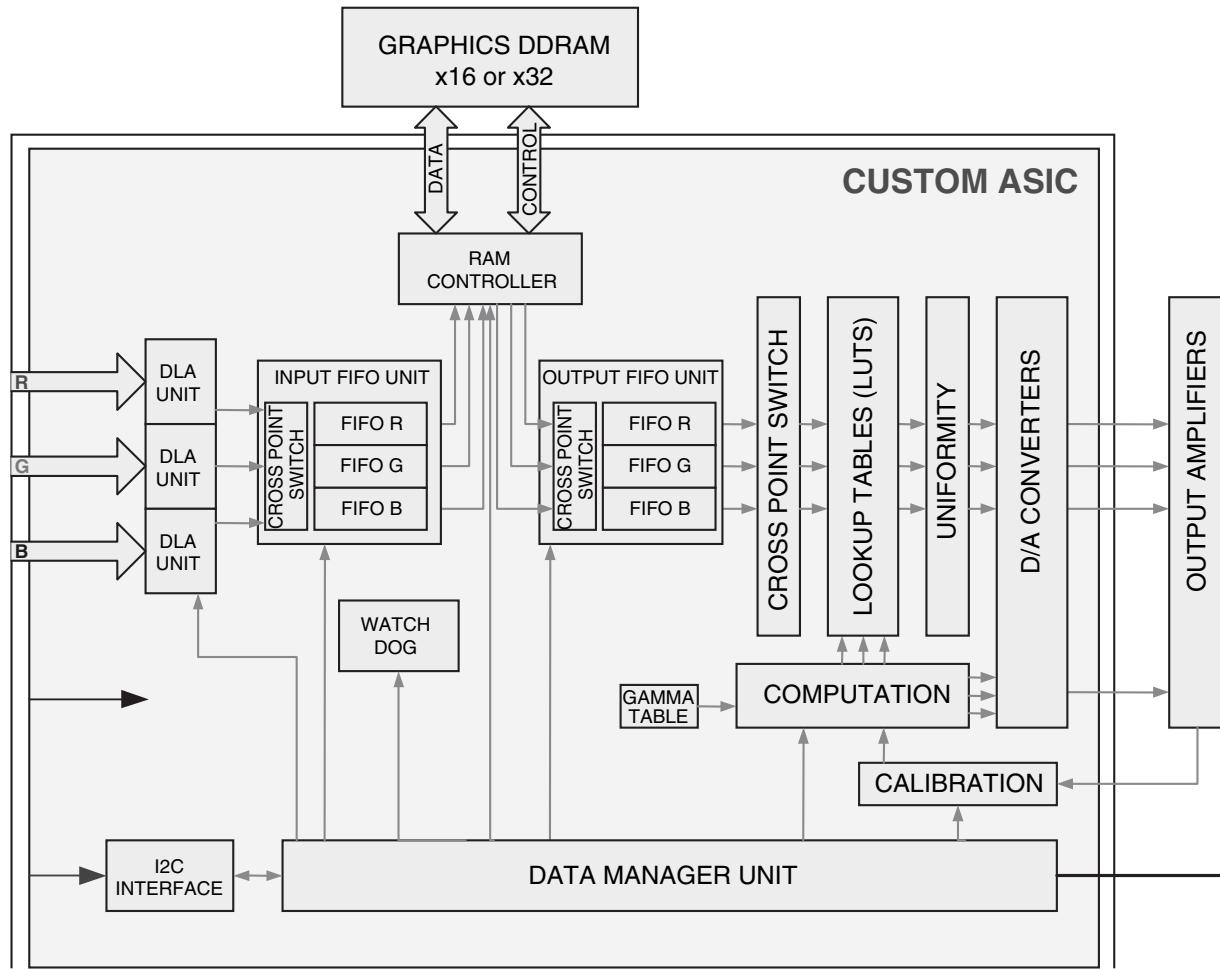

| 2.3 LCOS System Electronics Architecture                          | 40        |

| 2.3.1 Overview and Classification                                 | 40        |

| 2.3.2 Interface and Support Architecture                          | 41        |

| 2.3.3 Backplane Electronics                                       | 43        |

| 2.4 Analog Pixel Drive Schemes for Analog Electro-optic Response  | 52        |

| 2.4.1 Analog Voltage Addressing                                   | 52        |

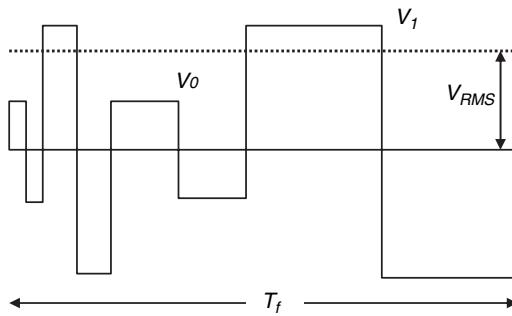

| 2.4.2 DC Balanced Driving of Liquid Crystal                       | 53        |

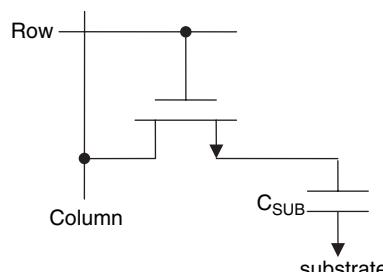

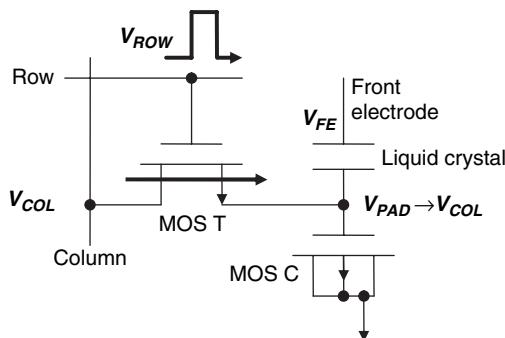

| 2.4.3 DRAM-style Analog Pixel                                     | 56        |

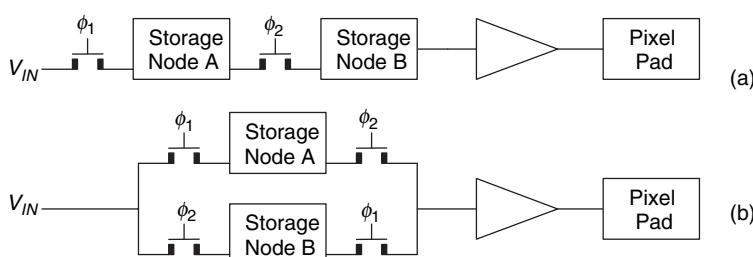

| 2.4.4 Frame Buffer Pixels for Analog Drive                        | 59        |

| 2.5 Digital Pixel Drive Schemes for Analog Electro-optic Response | 60        |

| 2.5.1 Nematic Liquid Crystal                                      | 60        |

| 2.5.2 Fringe Field Effects with Digital Drive                     | 63        |

| 2.5.3 Response Time Considerations for Digital Drive              | 63        |

| 2.6 Digital Pixel Drive Schemes for Binary Electro-optic Response | 64        |

| 2.6.1 Single Pulse Width Modulation                               | 65        |

| 2.6.2 Binary-Coded Pulse Width Modulation (B-PWM)                 | 66        |

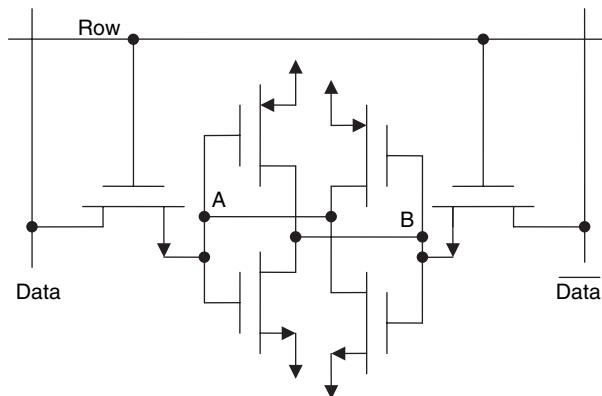

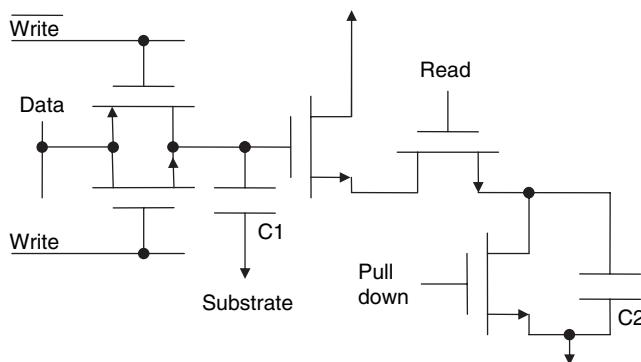

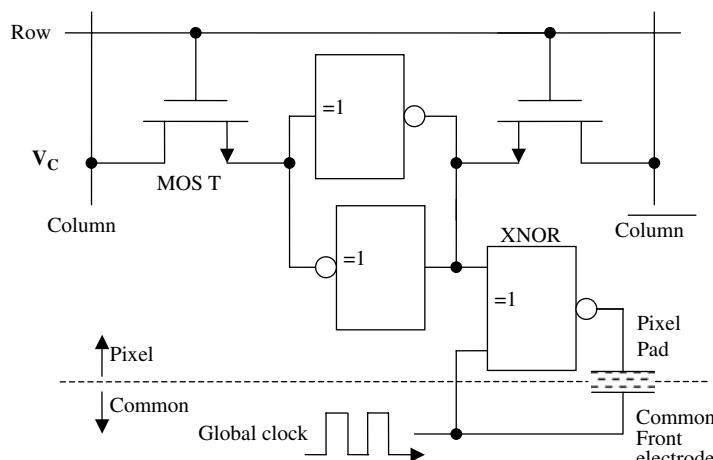

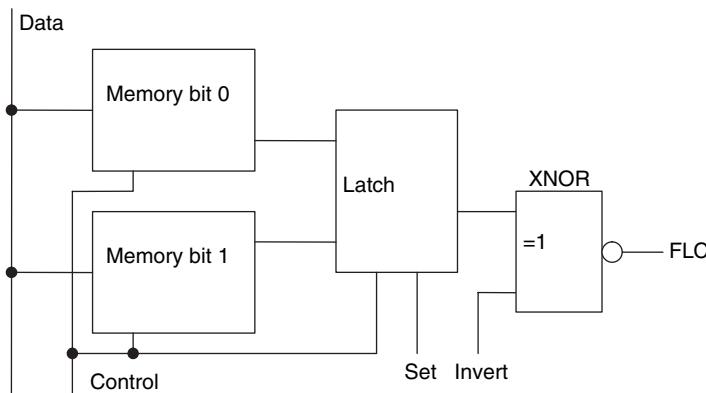

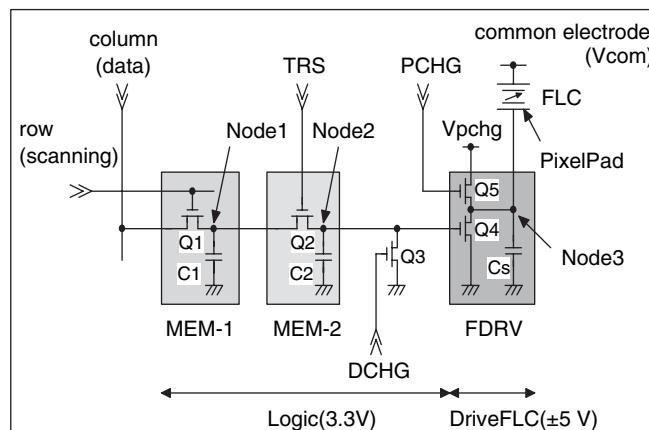

| 2.6.3 B-PWM Pixel Circuits                                        | 67        |

| 2.6.4 Grayscale Contouring                                        | 71        |

| 2.7 DMD Microdisplay Electronics                                  | 72        |

| 2.8 OLED Microdisplay Electronics                                 | 73        |

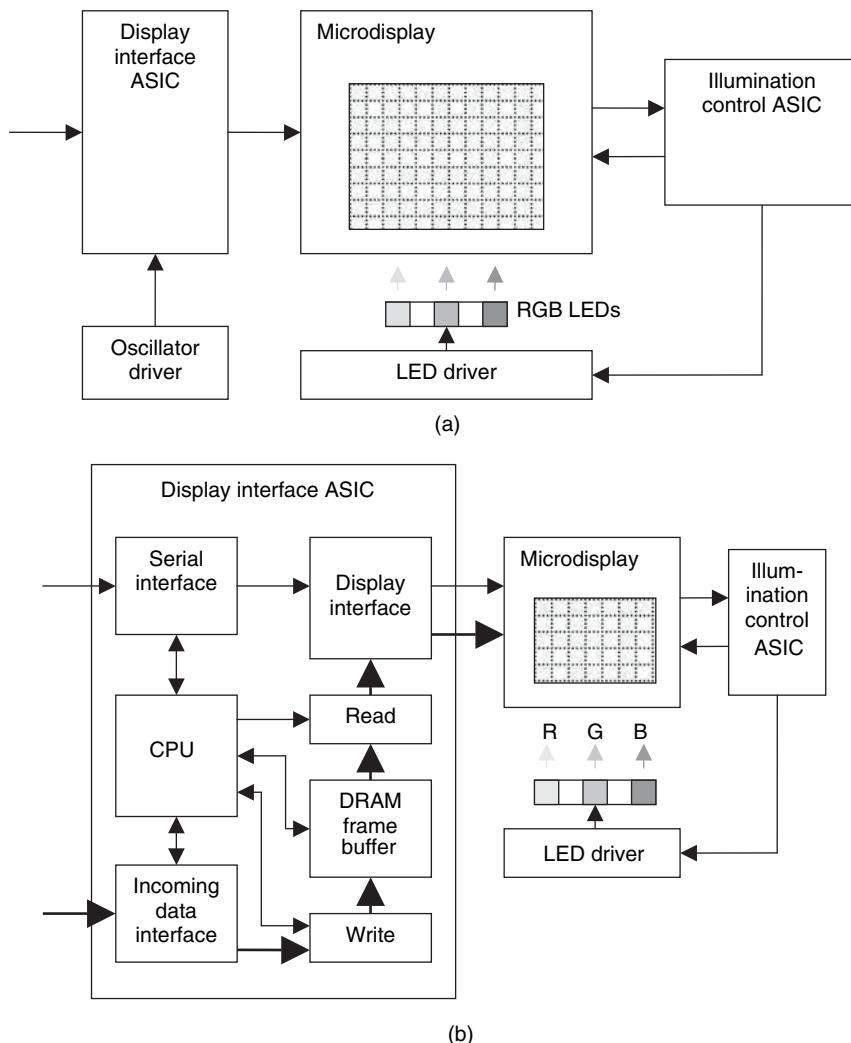

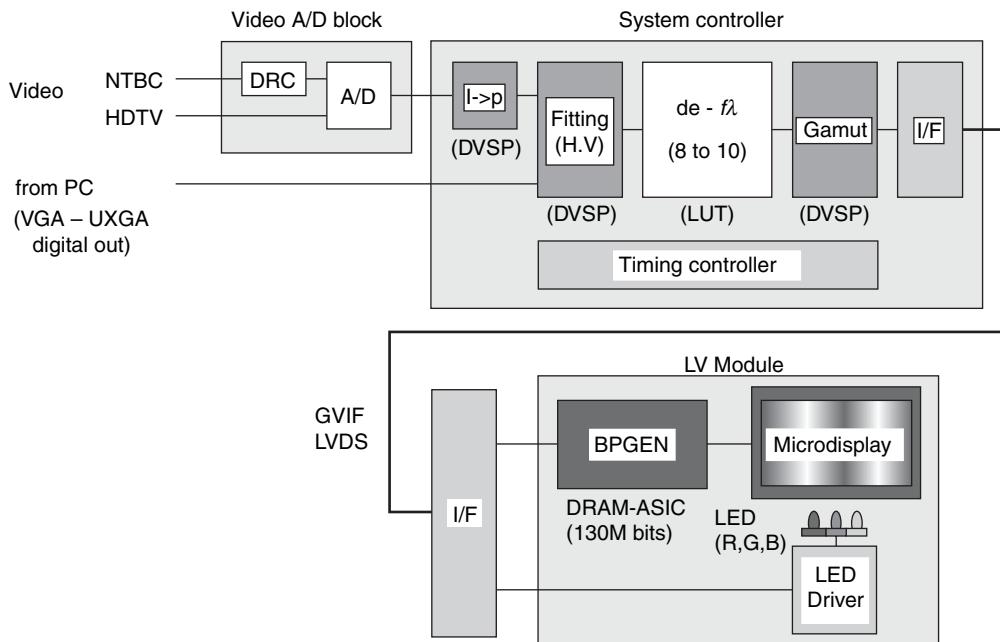

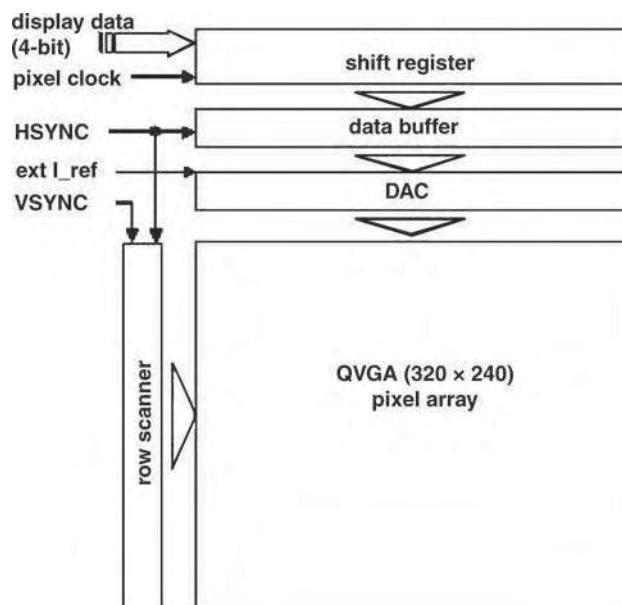

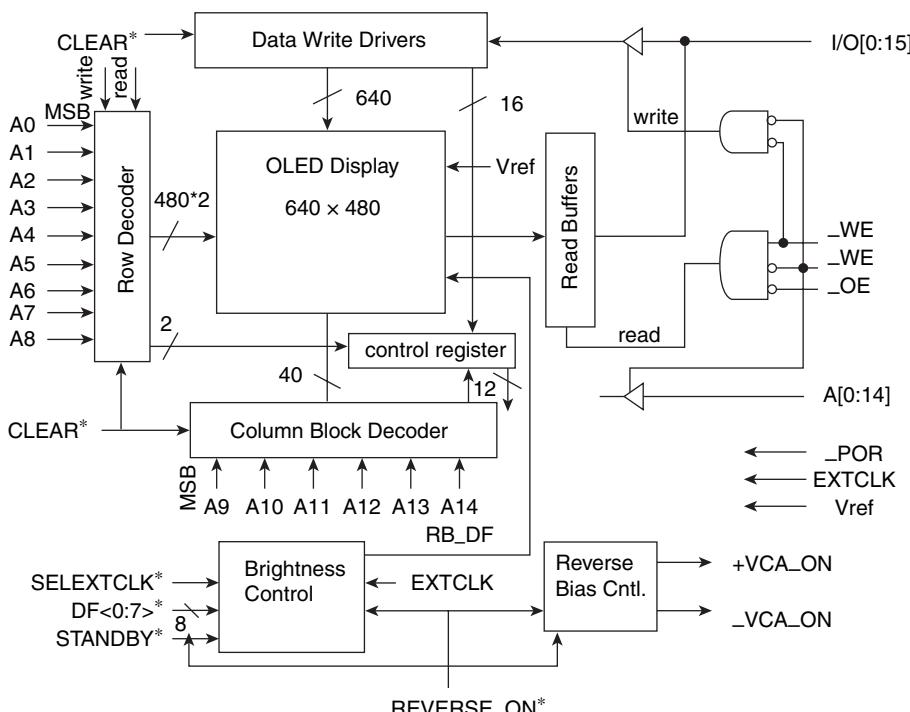

| 2.8.1 OLED Microdisplay System Overview                           | 73        |

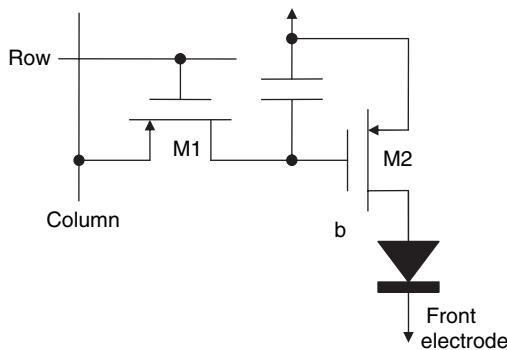

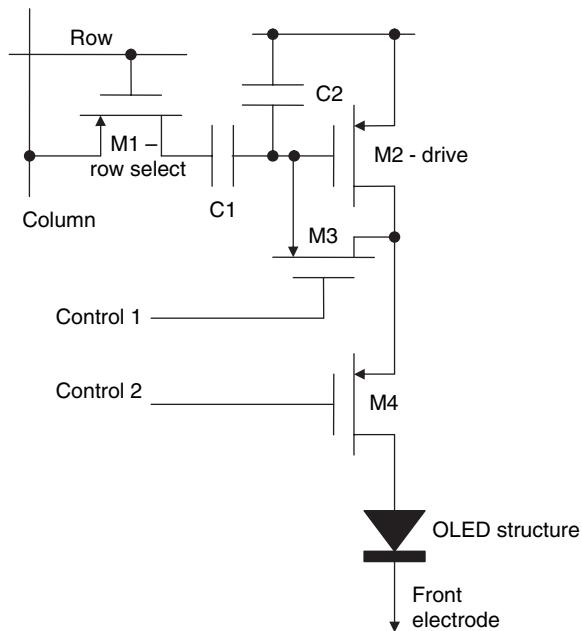

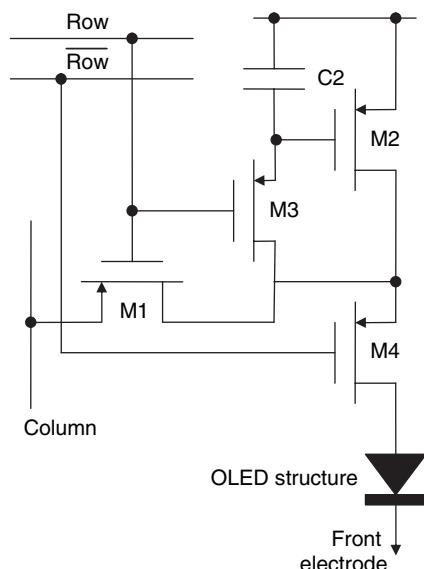

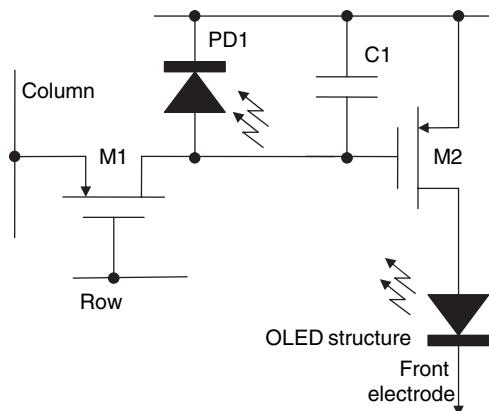

| 2.8.2 OLED Pixel Circuits using TFTs                              | 75        |

| 2.8.3 OLED Microdisplay with Digital Addressing: Example          | 77        |

| 2.8.4 OLED Microdisplay with Analog Addressing: Example           | 80        |

| 2.9 Photo-addressing                                              | 82        |

| 2.10 Bibliography                                                 | 83        |

| 2.11 References                                                   | 85        |

| <b>3. CMOS Backplane Technology</b>                               | <b>89</b> |

| 3.1 Introduction                                                  | 89        |

| 3.2 CMOS Technology                                               | 90        |

| 3.2.1 Background                                                  | 90        |

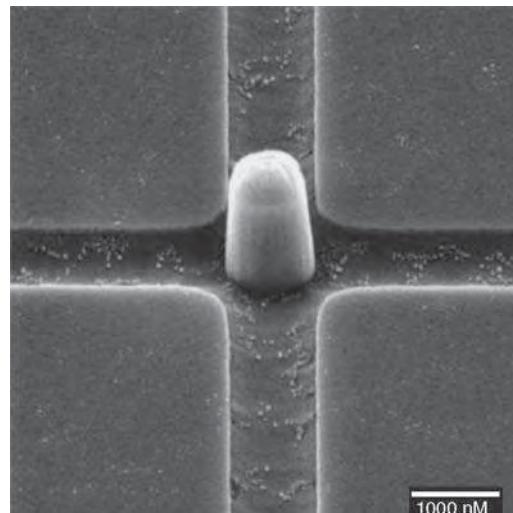

| 3.2.2 MOS Transistor Structure                                    | 91        |

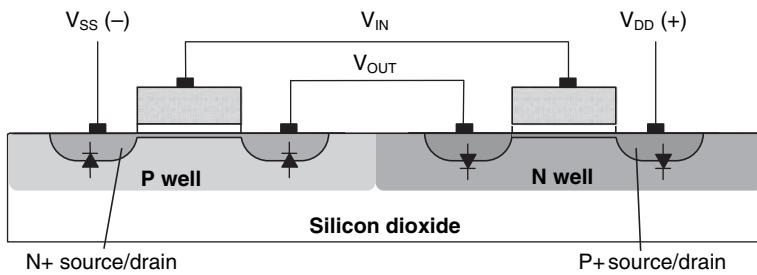

| 3.2.3 MOS Integrated Circuit Structure                            | 93        |

| 3.2.4 CMOS Fabrication Process                                    | 93        |

|           |                                              |            |

|-----------|----------------------------------------------|------------|

| 3.3       | CMOS for Microdisplays                       | 94         |

| 3.3.1     | Background                                   | 94         |

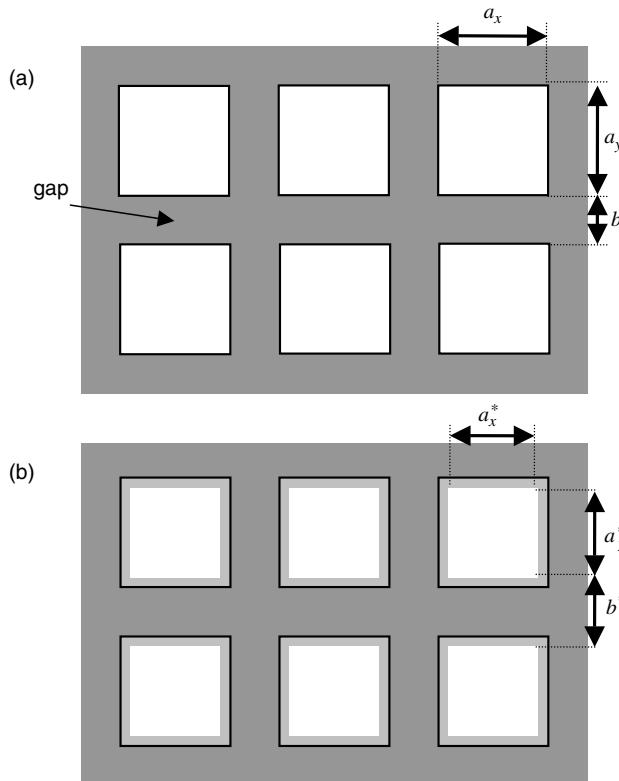

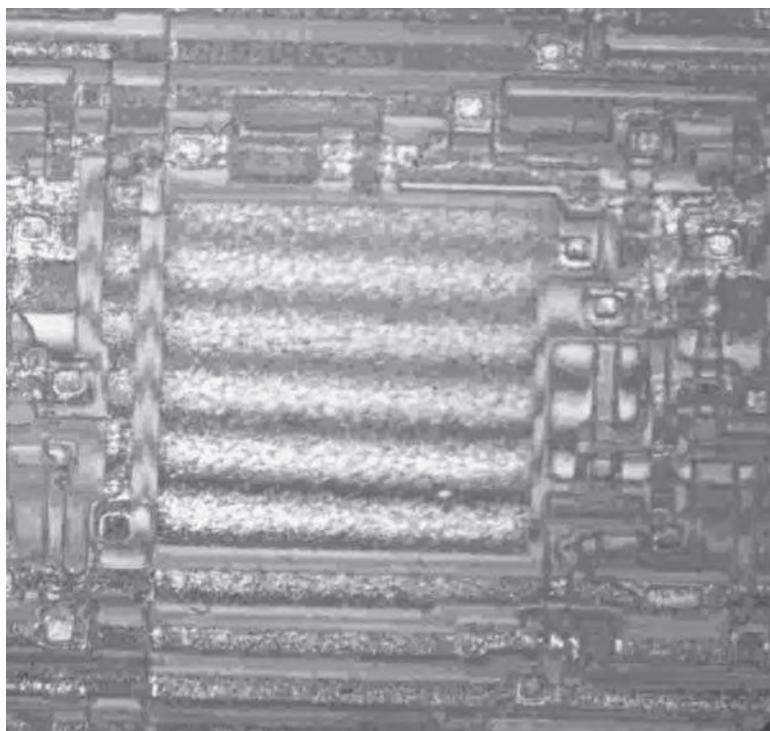

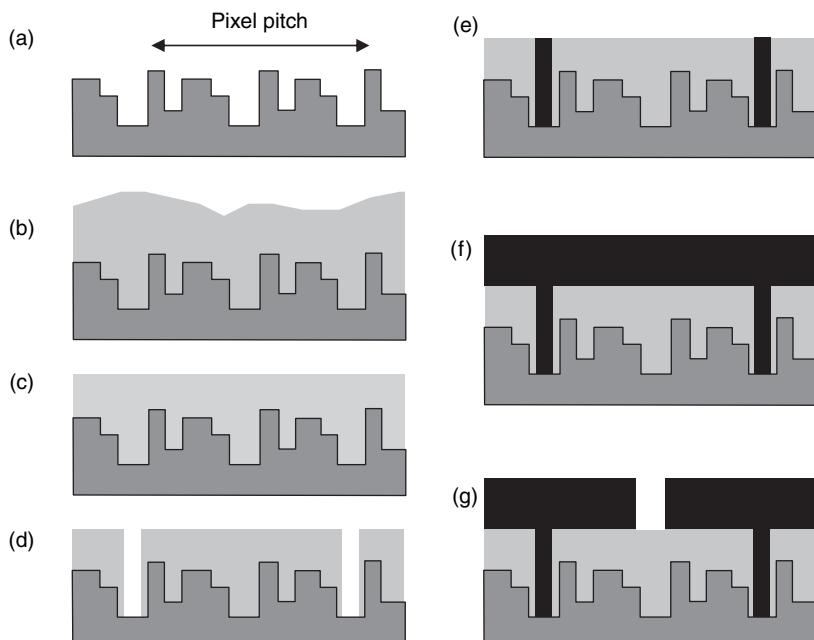

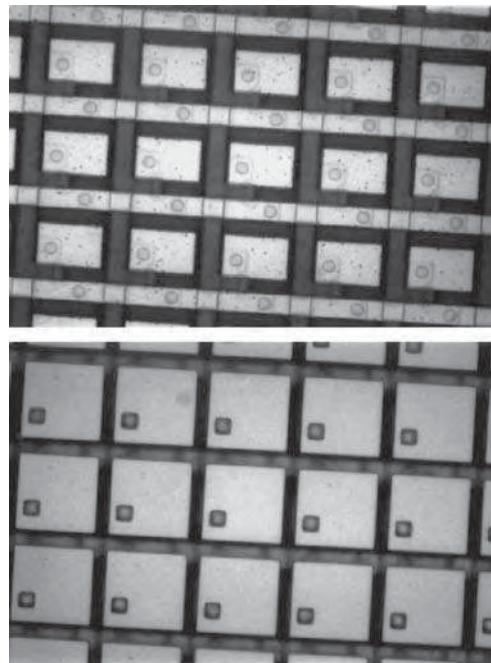

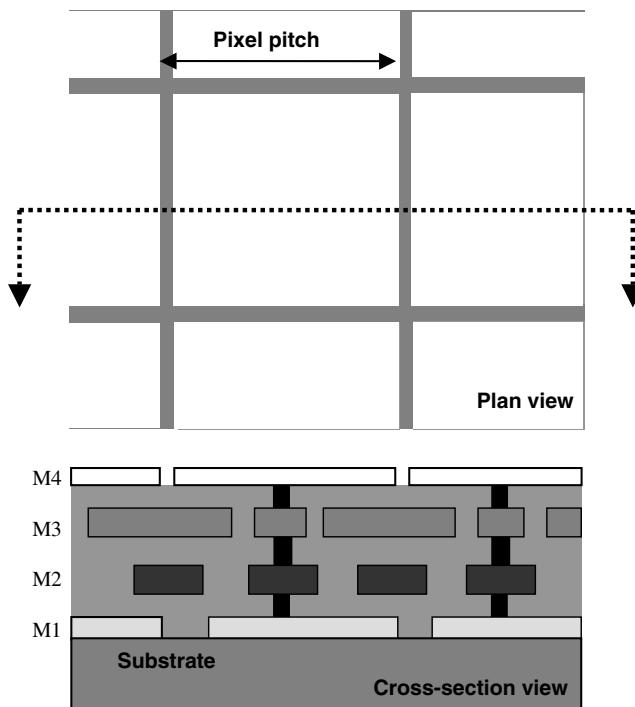

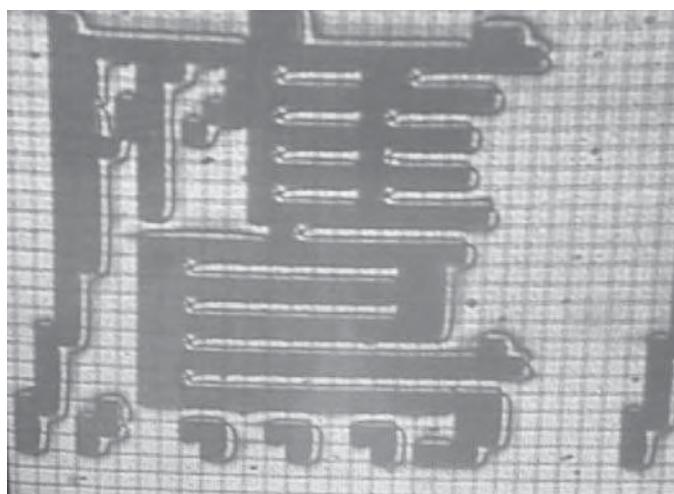

| 3.3.2     | Pixel Aperture Ratio                         | 96         |

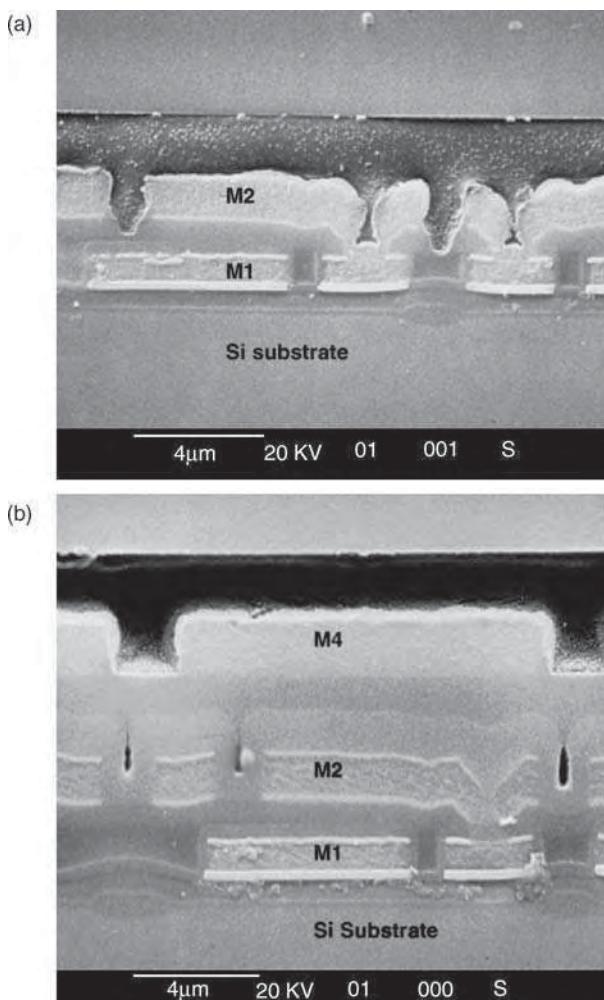

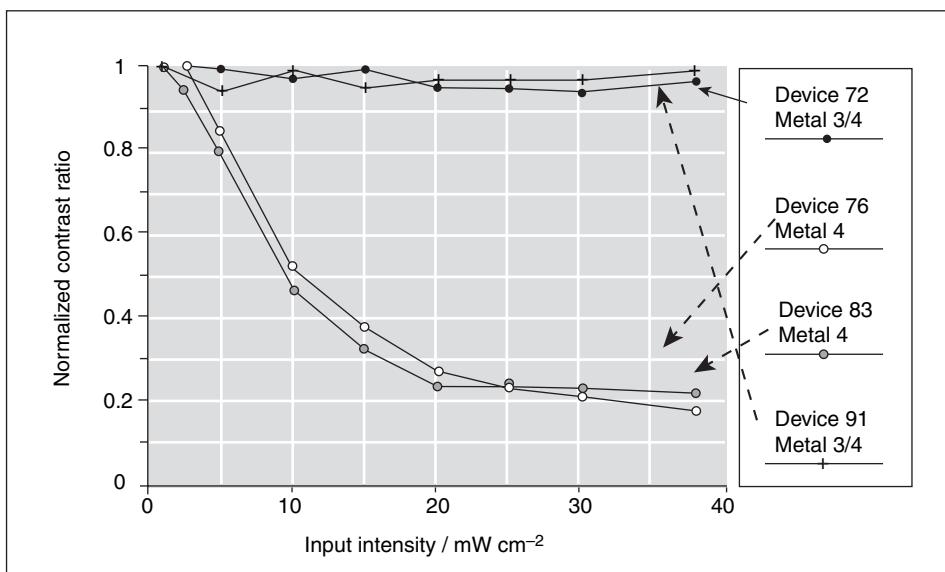

| 3.3.3     | Metal Layer Count                            | 97         |

| 3.3.4     | High-Voltage Structures                      | 99         |

| 3.3.5     | LCOS Microdisplays                           | 100        |

| 3.4       | Wafer and Die Bow                            | 100        |

| 3.4.1     | Wafer Flatness and Surface Metrology         | 102        |

| 3.5       | Wafer Surface Planarization                  | 102        |

| 3.5.1     | Introduction to Wafer Planarization          | 102        |

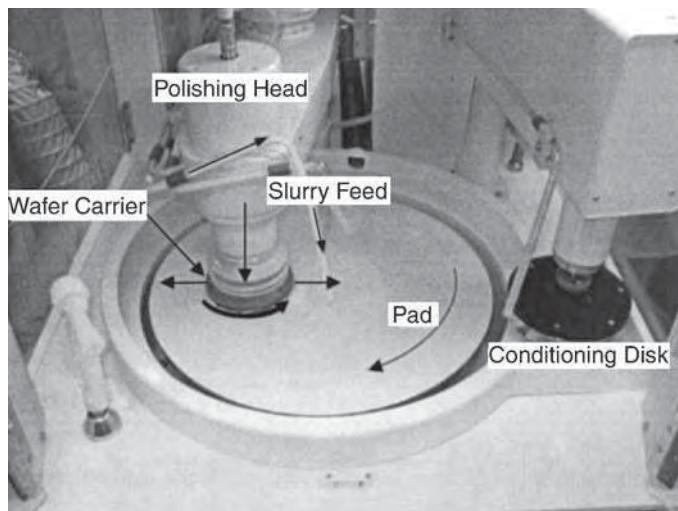

| 3.5.2     | Chemical Mechanical Polishing                | 104        |

| 3.5.3     | Damascene Polishing                          | 111        |

| 3.6       | Pixel Storage                                | 113        |

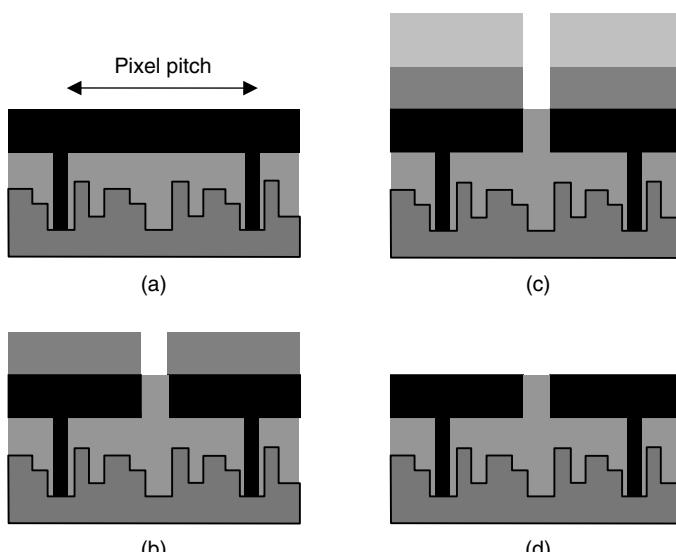

| 3.7       | Light Blocking                               | 114        |

| 3.8       | Mirror Quality                               | 117        |

| 3.9       | Pixel Gap Fill                               | 118        |

| 3.10      | LC Cell Thickness                            | 119        |

| 3.11      | LCOS CMOS Summary                            | 121        |

| 3.12      | Backplane Technology for Other Microdisplays | 123        |

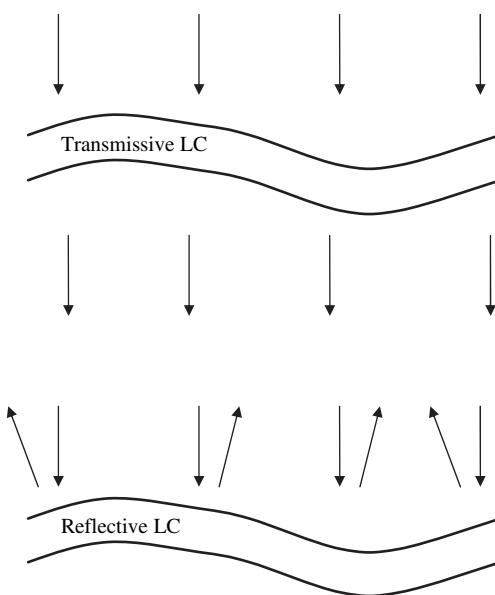

| 3.12.1    | Transmissive LCOS                            | 123        |

| 3.12.2    | Micro-optical-electromechanical Systems      | 124        |

| 3.12.3    | OLED CMOS                                    | 124        |

| 3.13      | Silicon Technology Roadmap                   | 125        |

| 3.14      | Cost of Silicon                              | 126        |

| 3.14.1    | Wafer Cost                                   | 126        |

| 3.14.2    | Yield                                        | 127        |

| 3.14.3    | Qualitative Yield Comparisons                | 127        |

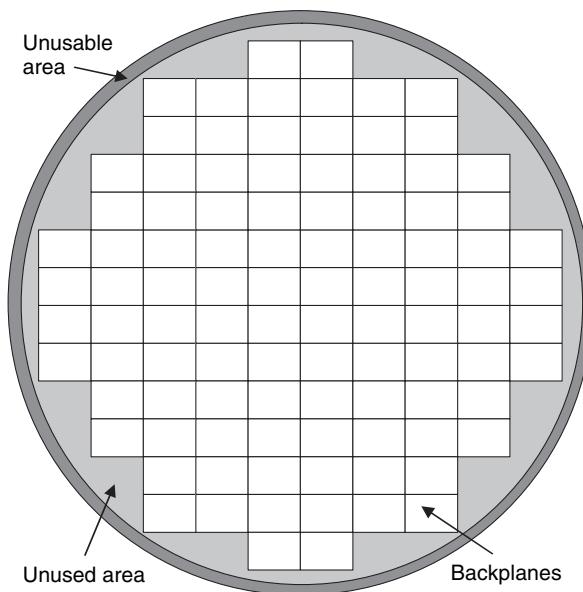

| 3.14.4    | Good Dice per Wafer                          | 128        |

| 3.14.5    | Cost per Good Die                            | 128        |

| 3.15      | Summary                                      | 130        |

| 3.16      | Bibliography                                 | 130        |

| 3.17      | References                                   | 132        |

| <b>4.</b> | <b>Transmission Microdisplay Structure</b>   | <b>135</b> |

| 4.1       | Background                                   | 135        |

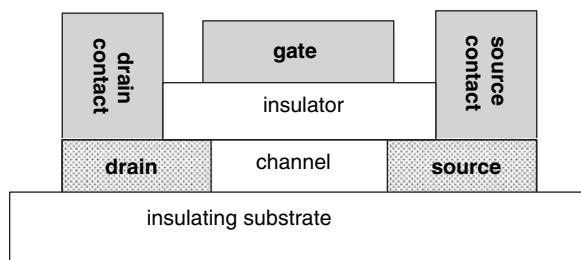

| 4.2       | Thin Film Transistors                        | 136        |

| 4.3       | Polysilicon                                  | 137        |

| 4.3.1     | Background                                   | 137        |

| 4.3.2     | Preparation                                  | 138        |

| 4.4       | Polysilicon LC Microdisplay                  | 138        |

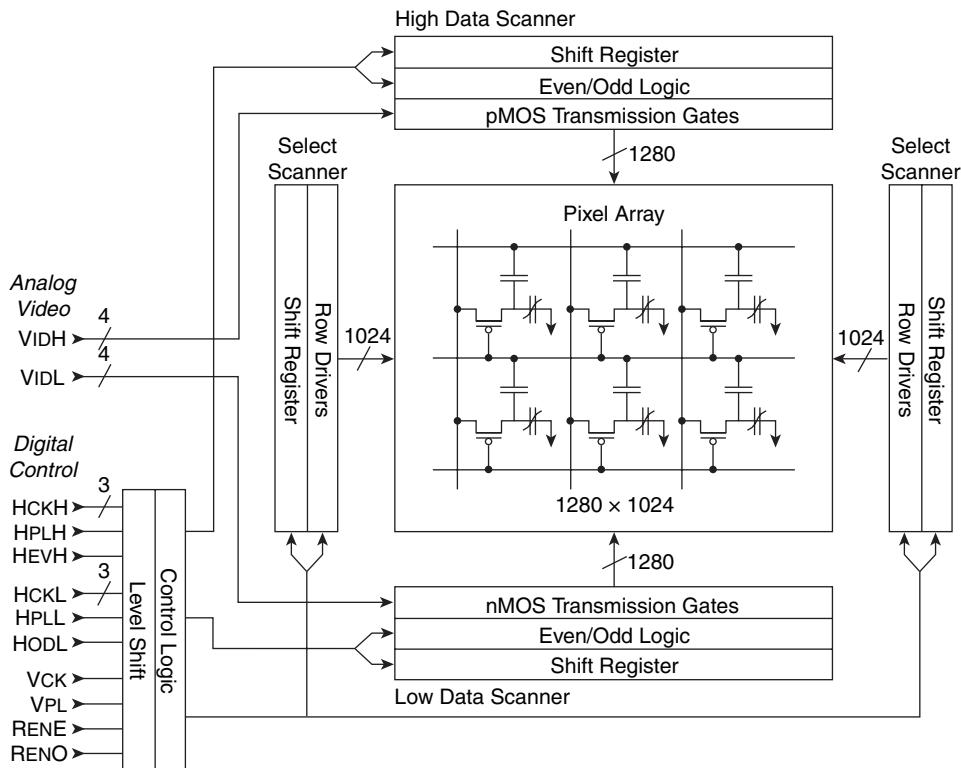

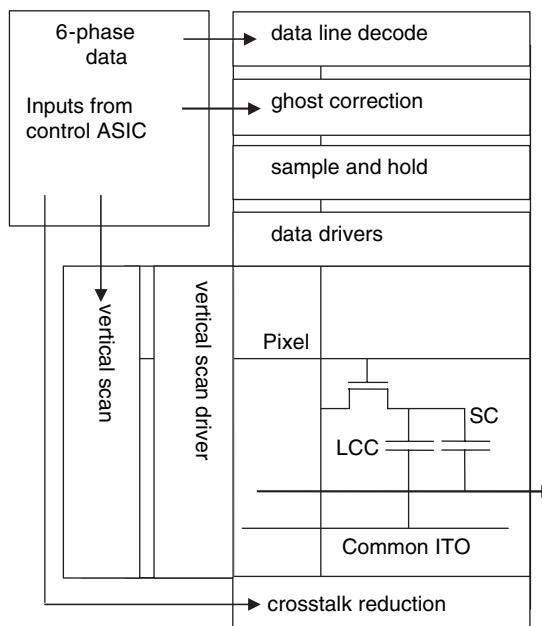

| 4.4.1     | Matrix Addressing                            | 138        |

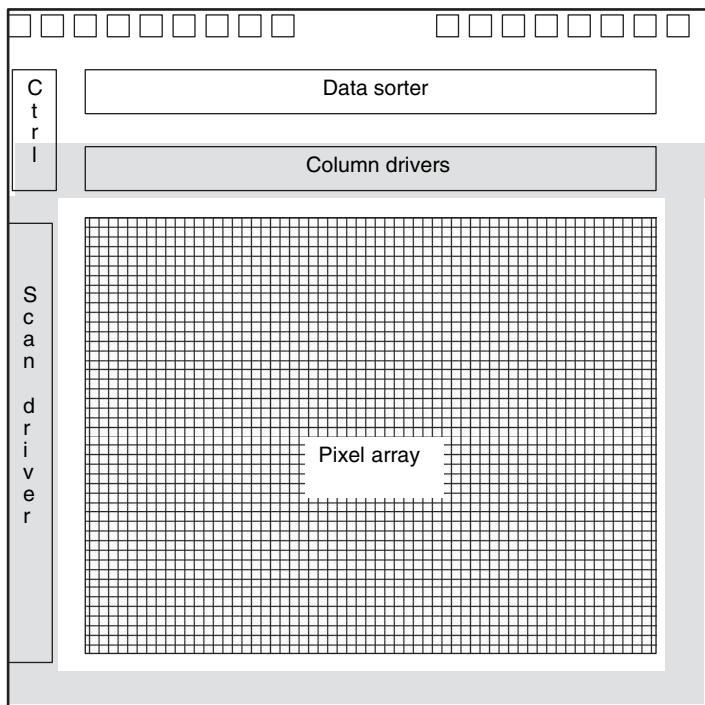

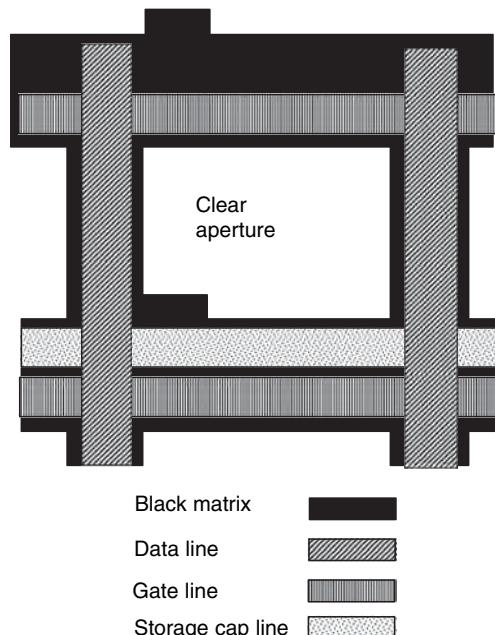

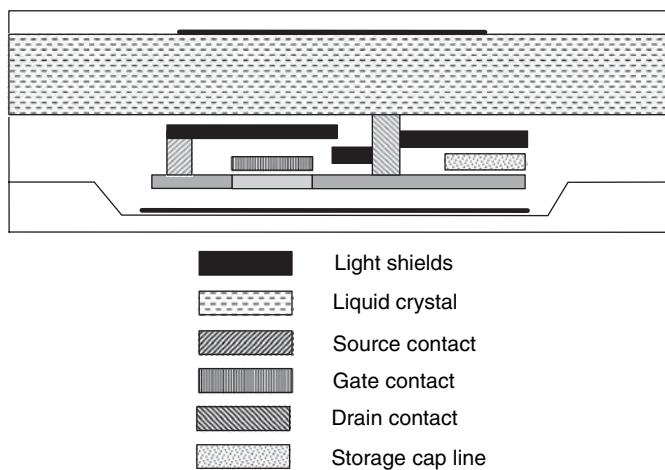

| 4.4.2     | Physical Layout                              | 140        |

| 4.4.3     | Aperture Ratio                               | 141        |

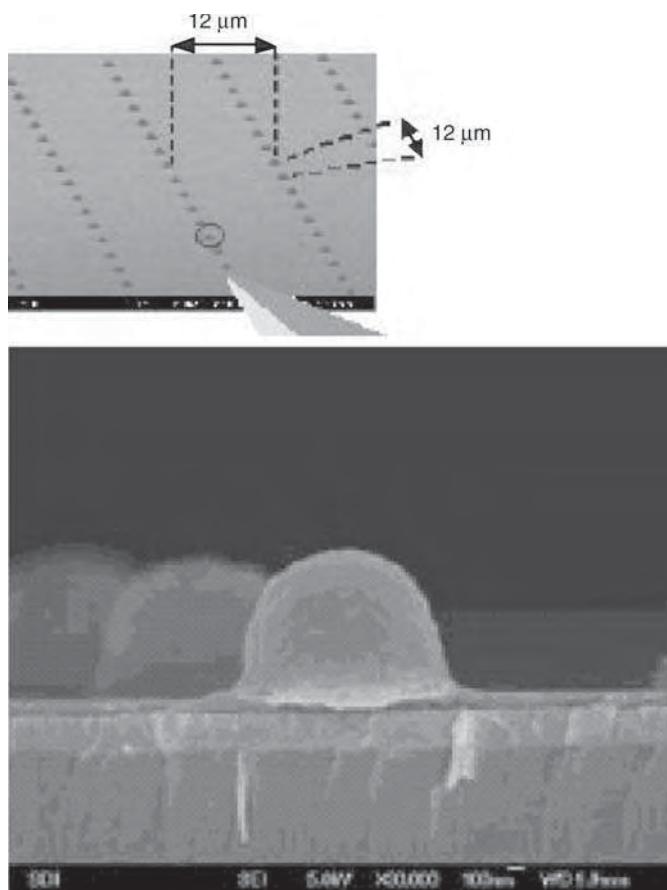

| 4.4.4     | Microlens Array                              | 142        |

| 4.4.5     | Performance                                  | 143        |

| 4.4.6     | Recent Developments                          | 144        |

| 4.5       | Transferred Silicon                          | 145        |

| 4.5.1     | Concept                                      | 145        |

| 4.5.2     | Process                                      | 146        |

| 4.5.3     | Performance                                  | 146        |

|           |                                                  |            |

|-----------|--------------------------------------------------|------------|

| 4.6       | Silicon-on-Sapphire                              | 146        |

| 4.7       | Closing Comment                                  | 147        |

| 4.8       | References                                       | 147        |

| <b>5.</b> | <b>Transmissive Liquid Crystal Microdisplays</b> | <b>149</b> |

| 5.1       | Introduction                                     | 149        |

| 5.2       | TFT-LCD                                          | 149        |

| 5.3       | Projection System                                | 151        |

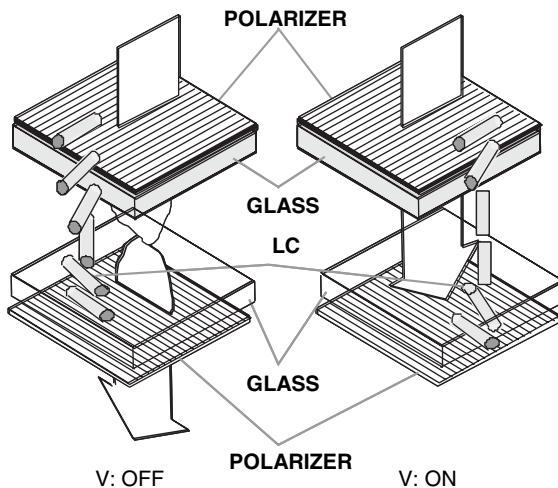

| 5.4       | Twisted Nematic Cells                            | 152        |

| 5.4.1     | Jones Matrices                                   | 153        |

| 5.4.2     | Viewing Angle                                    | 155        |

| 5.5       | Vertically Aligned Nematic (VAN) Cells           | 155        |

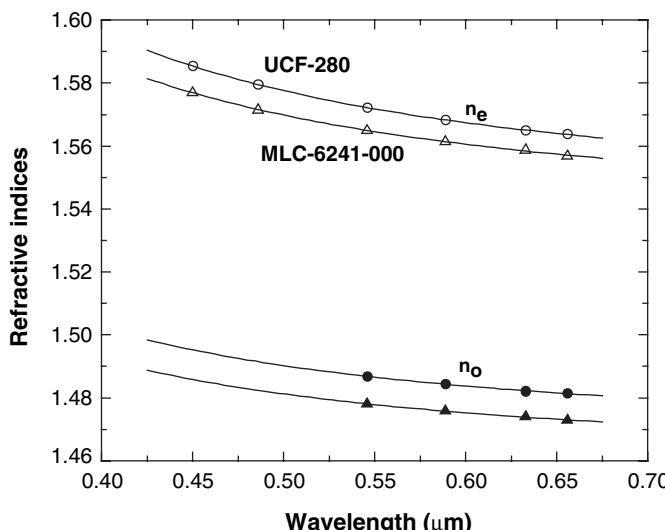

| 5.5.1     | LC Alignment                                     | 156        |

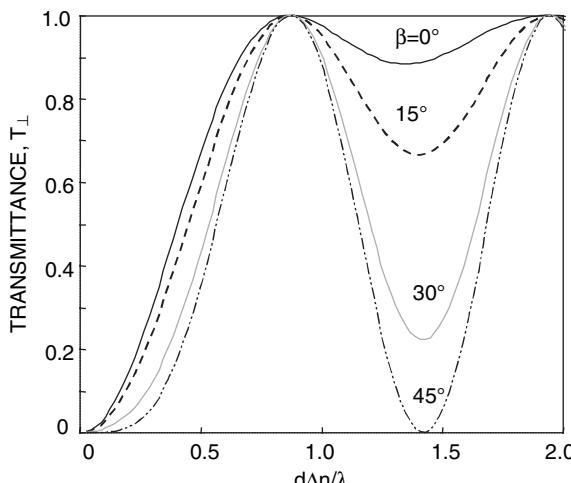

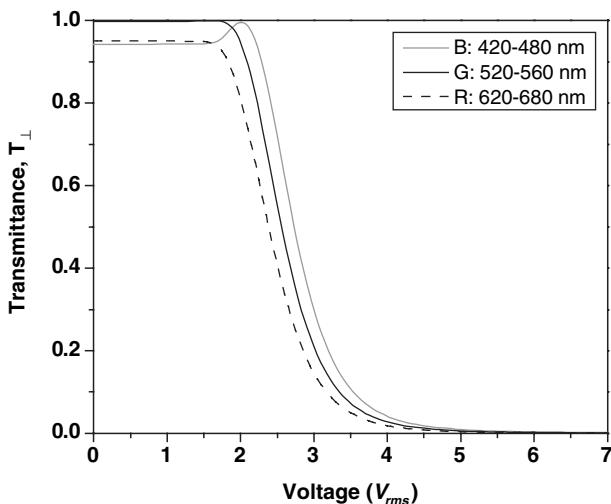

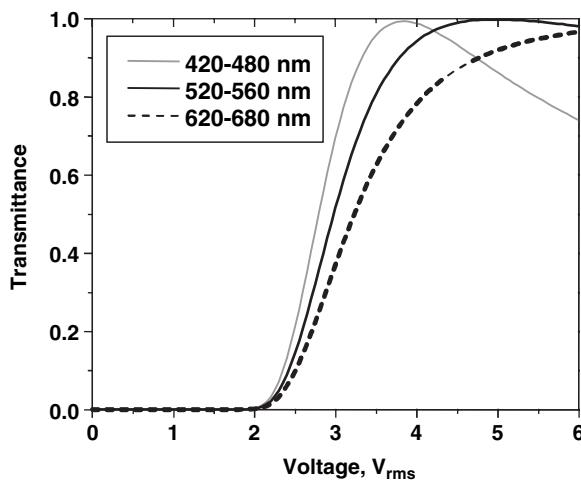

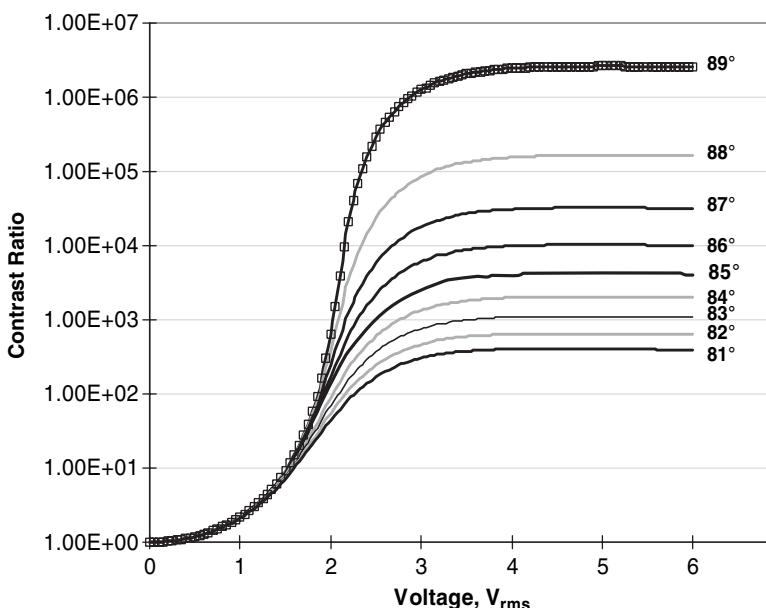

| 5.5.2     | Electro-optic Effects                            | 159        |

| 5.5.3     | Response Time                                    | 164        |

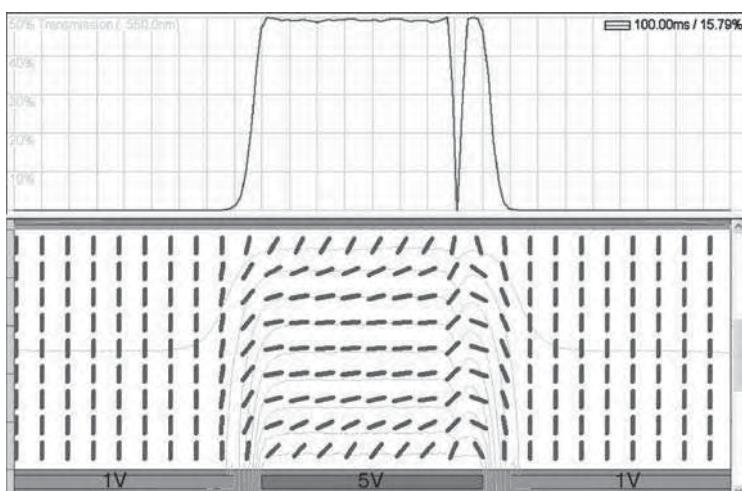

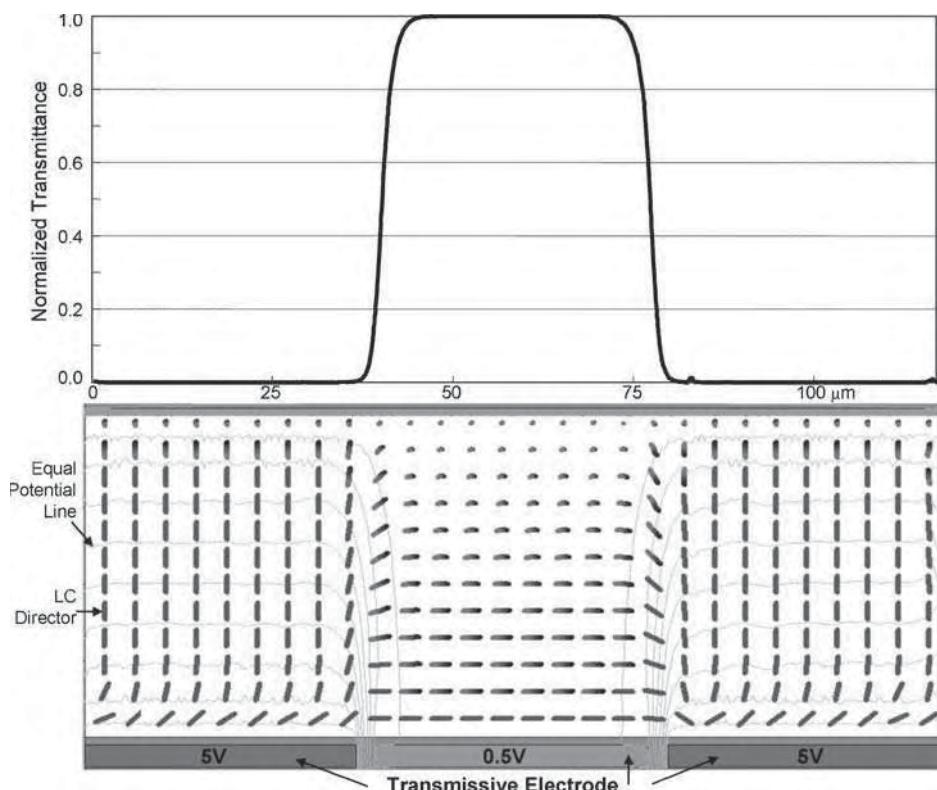

| 5.6       | Fringing Field Effect                            | 165        |

| 5.7       | Liquid Crystal Ionic Effects                     | 166        |

| 5.7.1     | Ionic Conduction                                 | 167        |

| 5.7.2     | Space Charge                                     | 168        |

| 5.7.3     | Image Sticking                                   | 169        |

| 5.7.4     | Electrode Effects                                | 170        |

| 5.8       | References                                       | 170        |

| <b>6.</b> | <b>Reflective Liquid Crystal Microdisplays</b>   | <b>173</b> |

| 6.1       | Introduction                                     | 173        |

| 6.2       | Normally Black Homeotropic Cell                  | 176        |

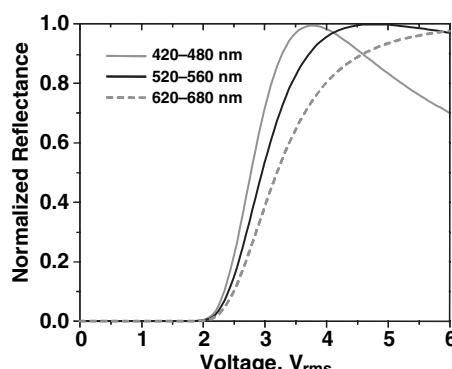

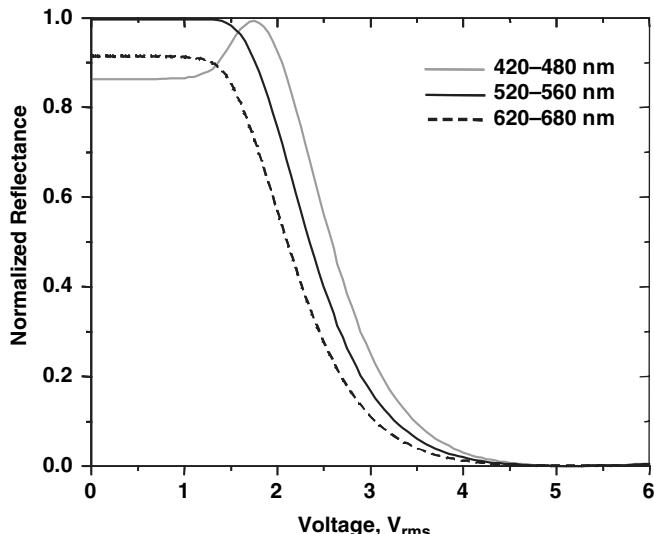

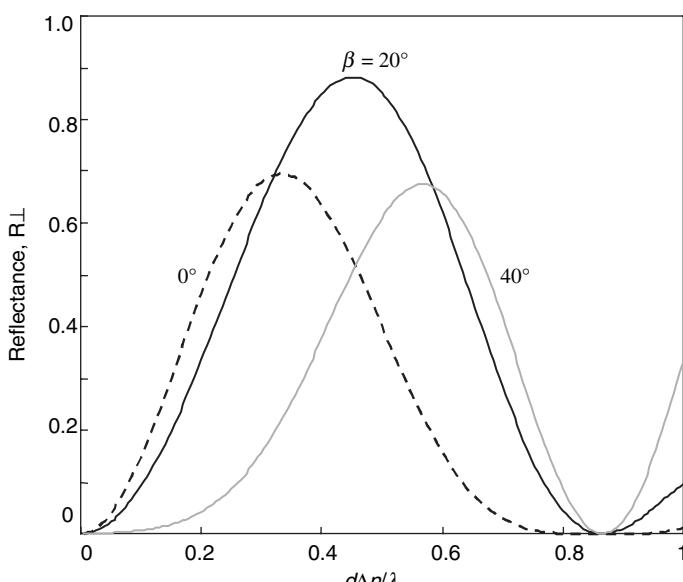

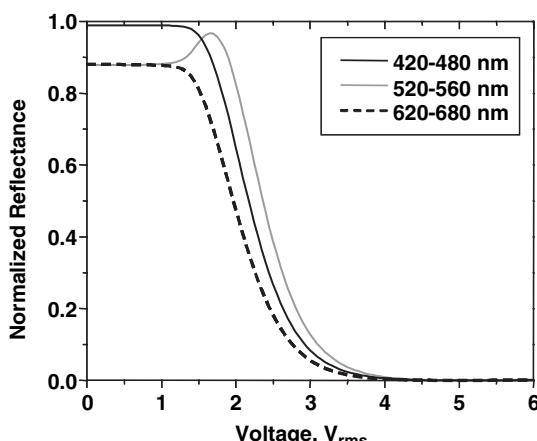

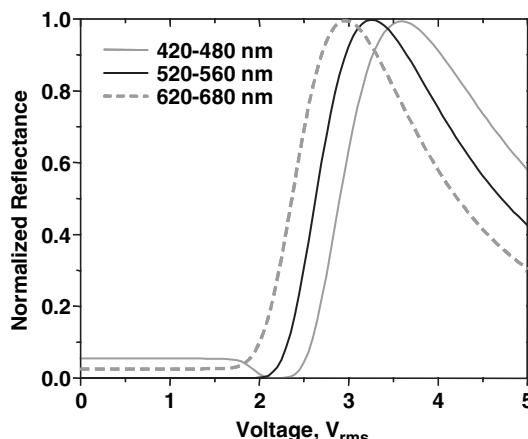

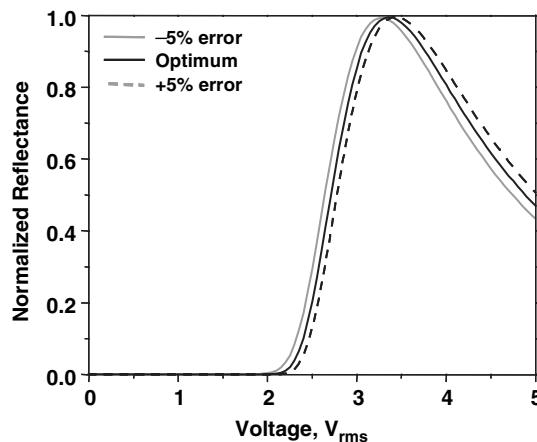

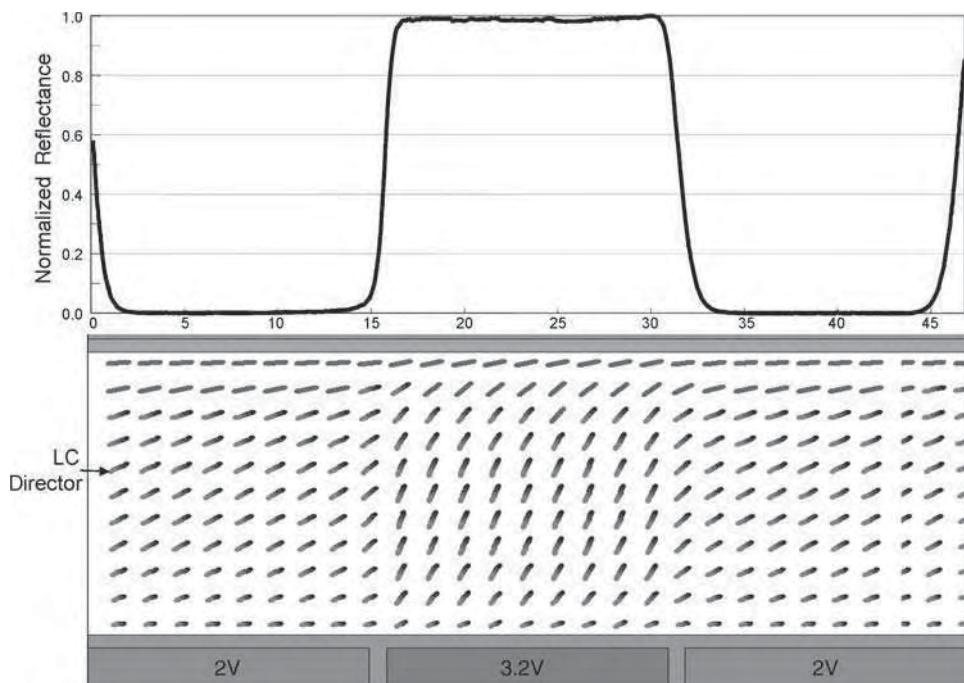

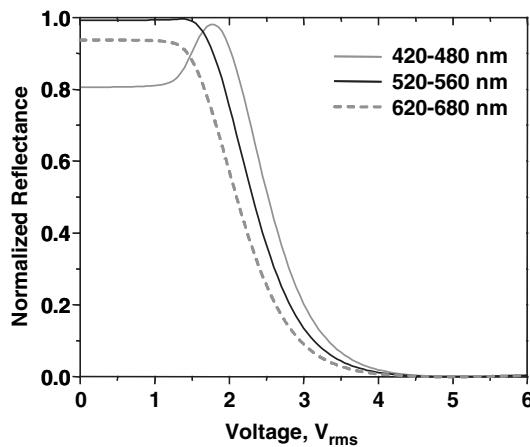

| 6.2.1     | Voltage-dependent Reflectance                    | 176        |

| 6.2.2     | Pretilt Angle Effect                             | 178        |

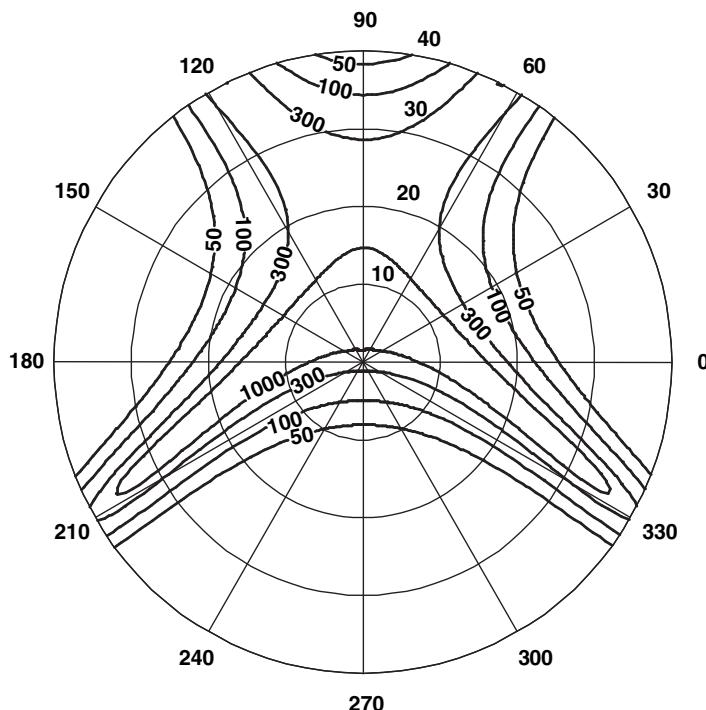

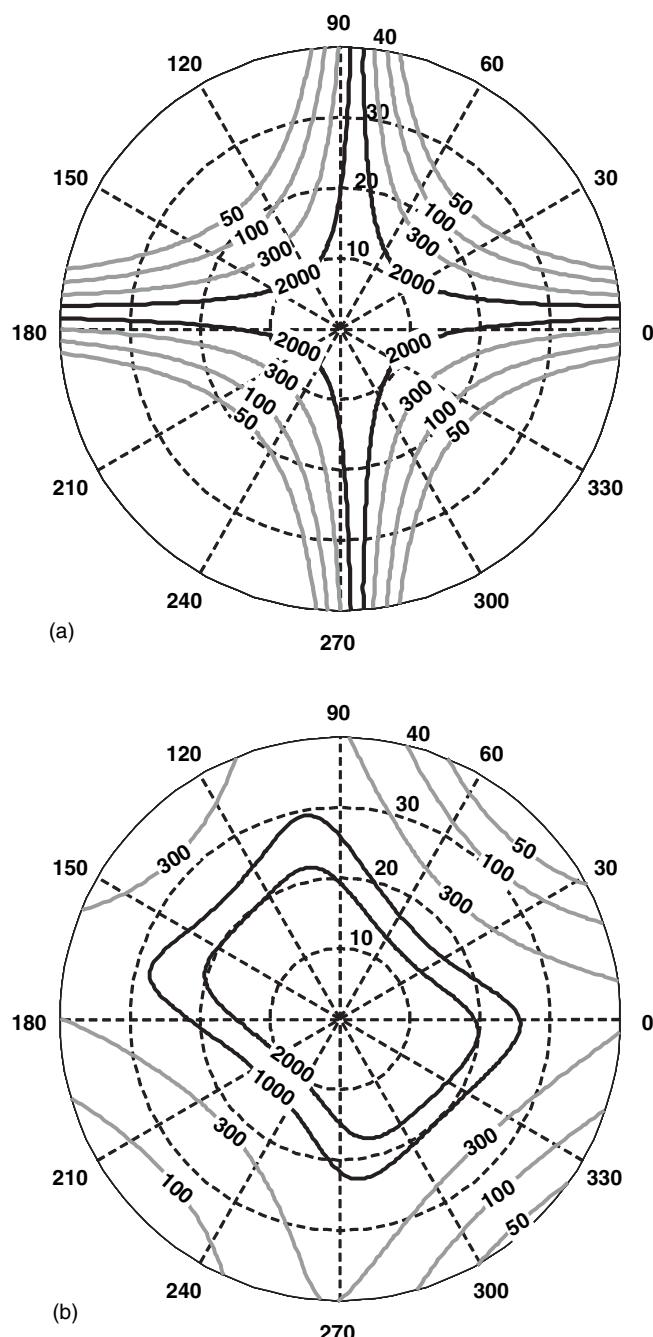

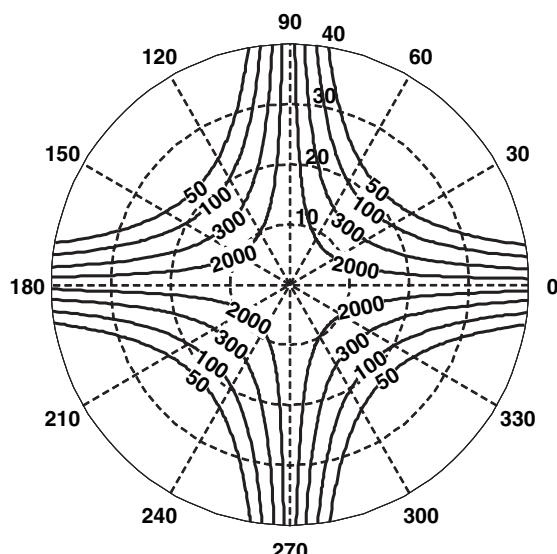

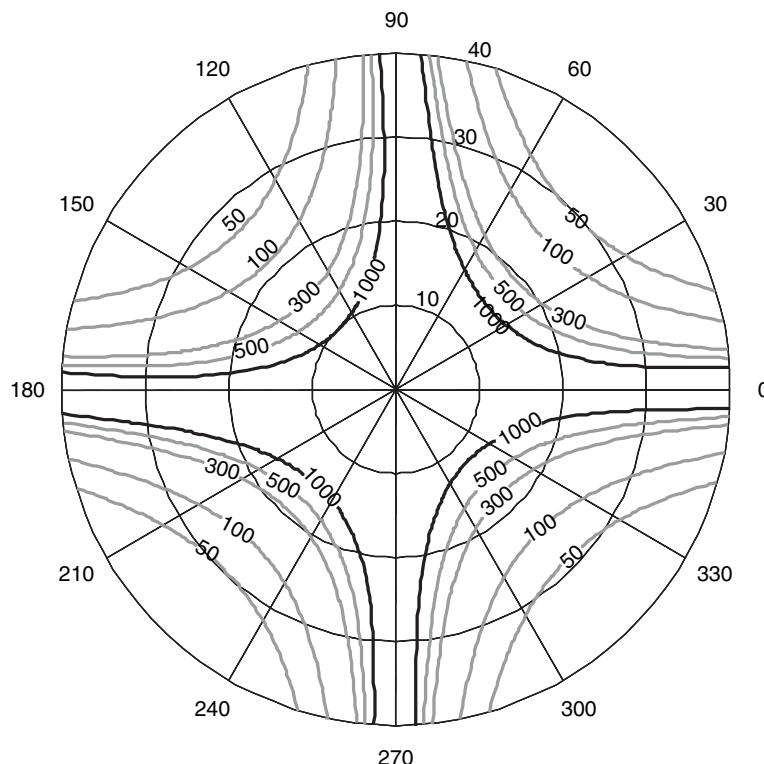

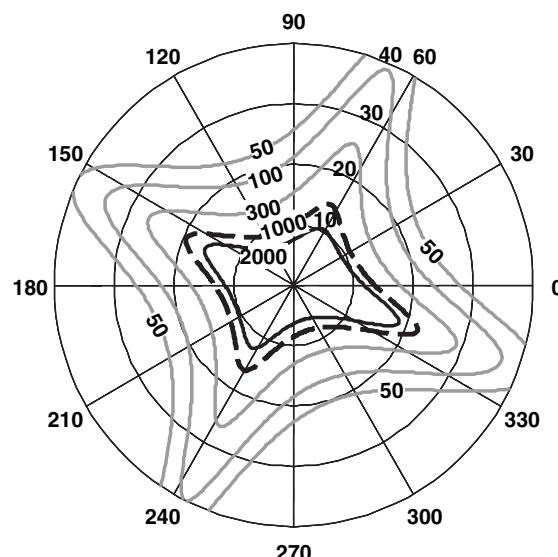

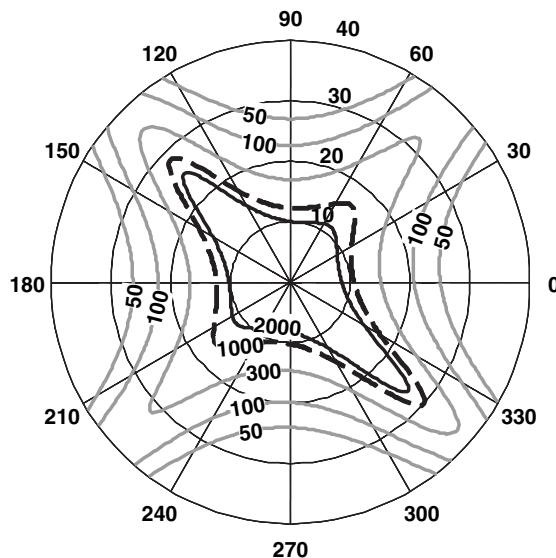

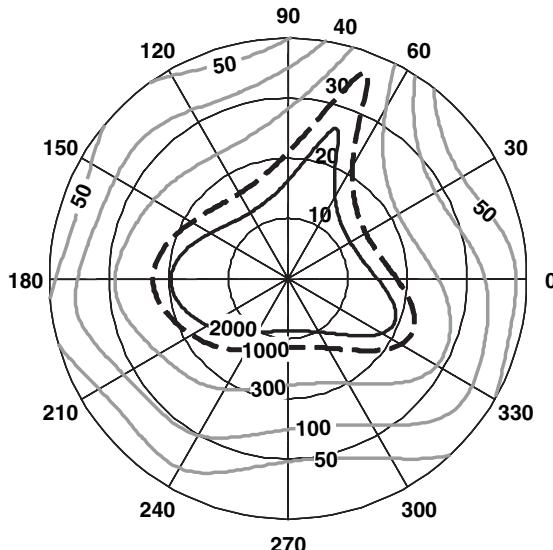

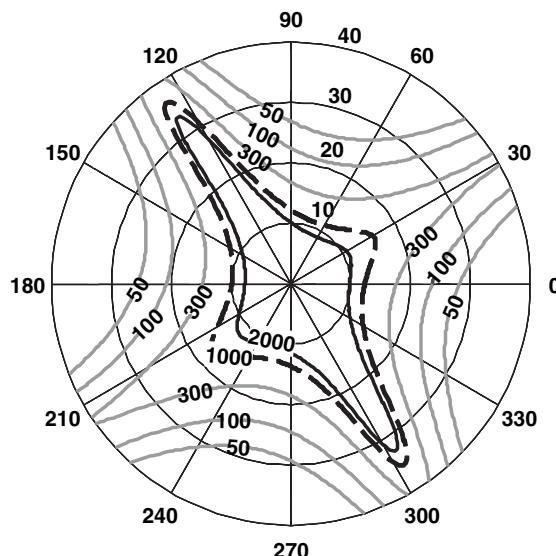

| 6.2.3     | Viewing Cone                                     | 178        |

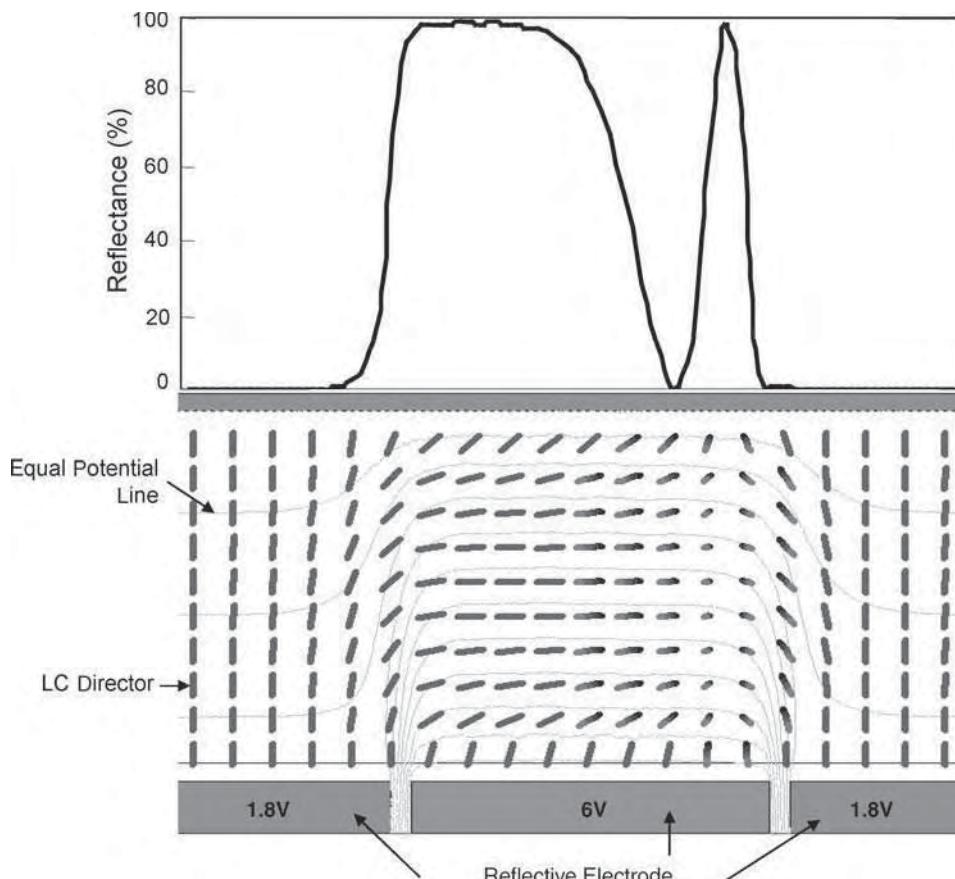

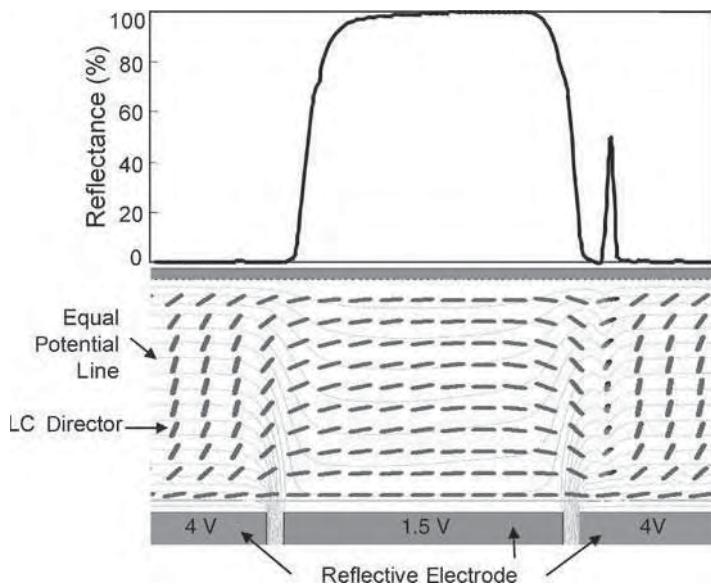

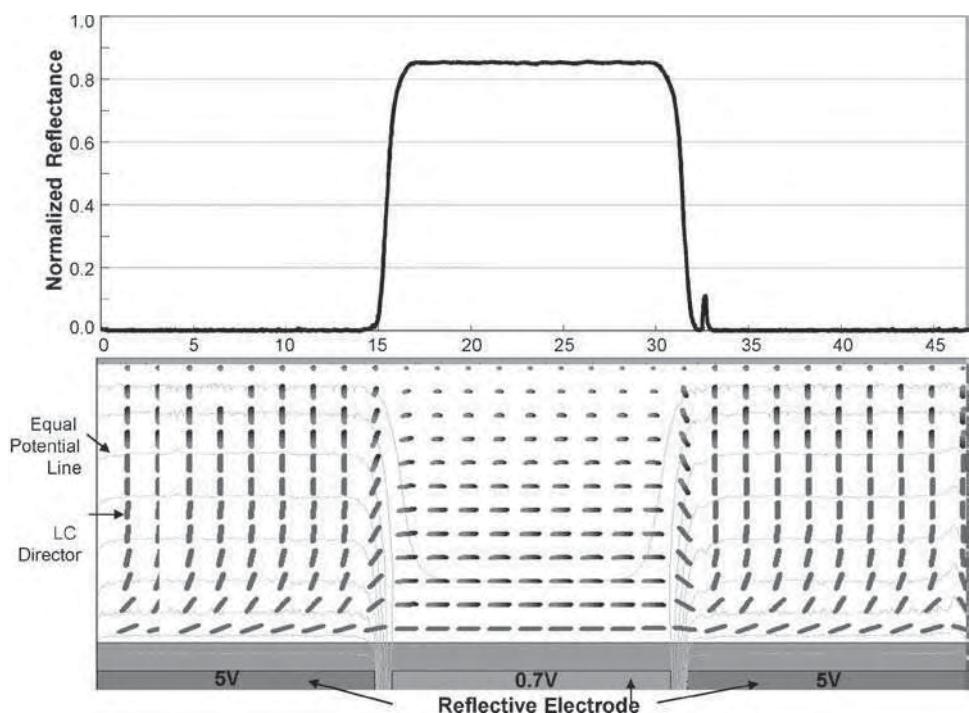

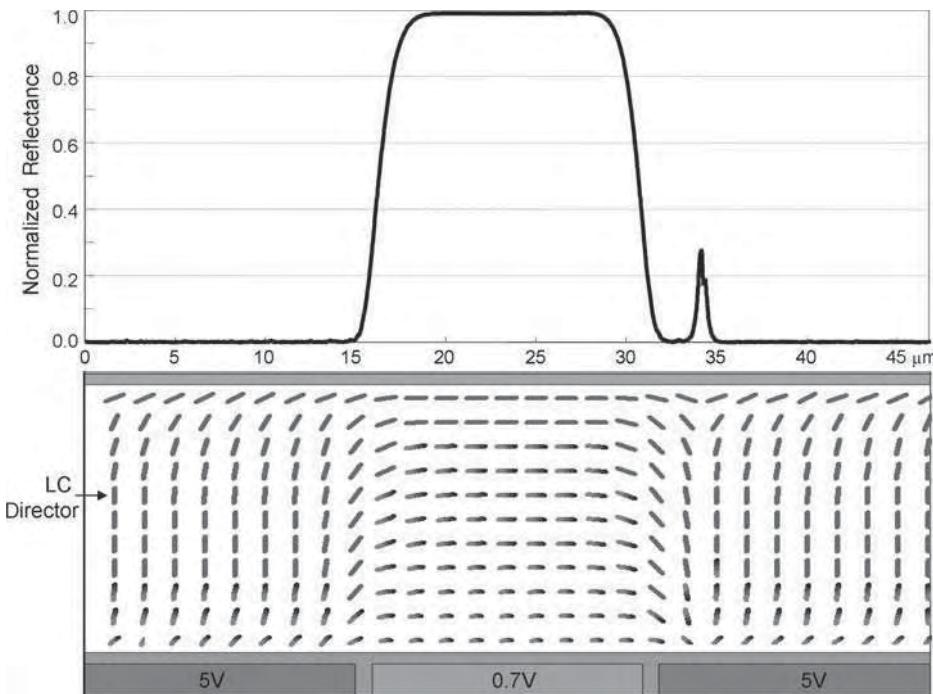

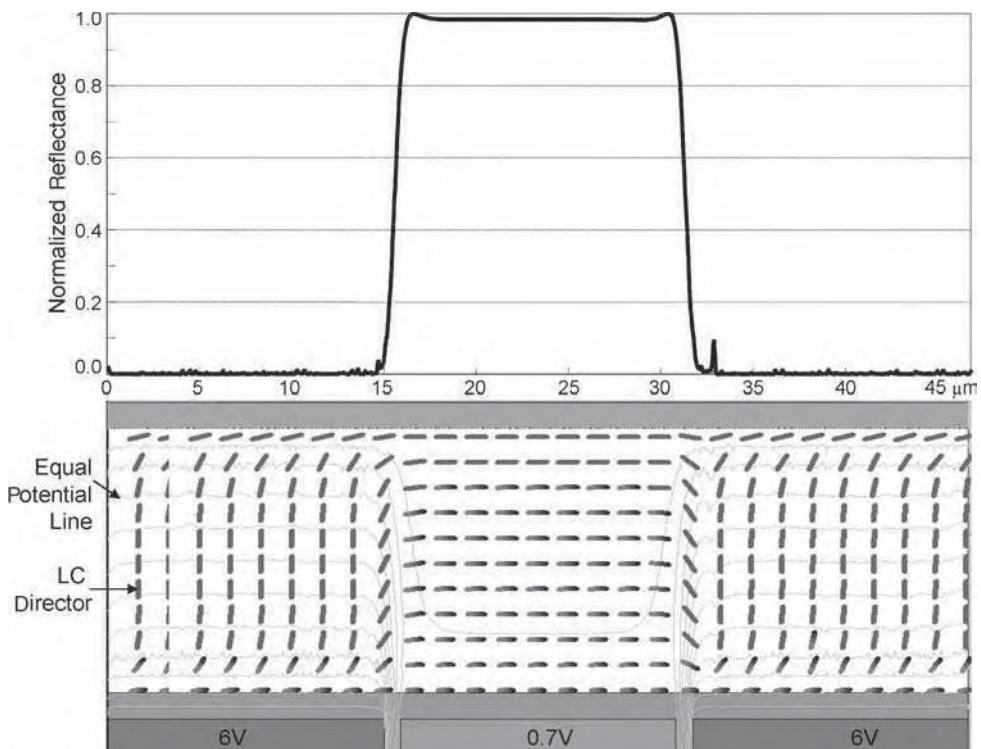

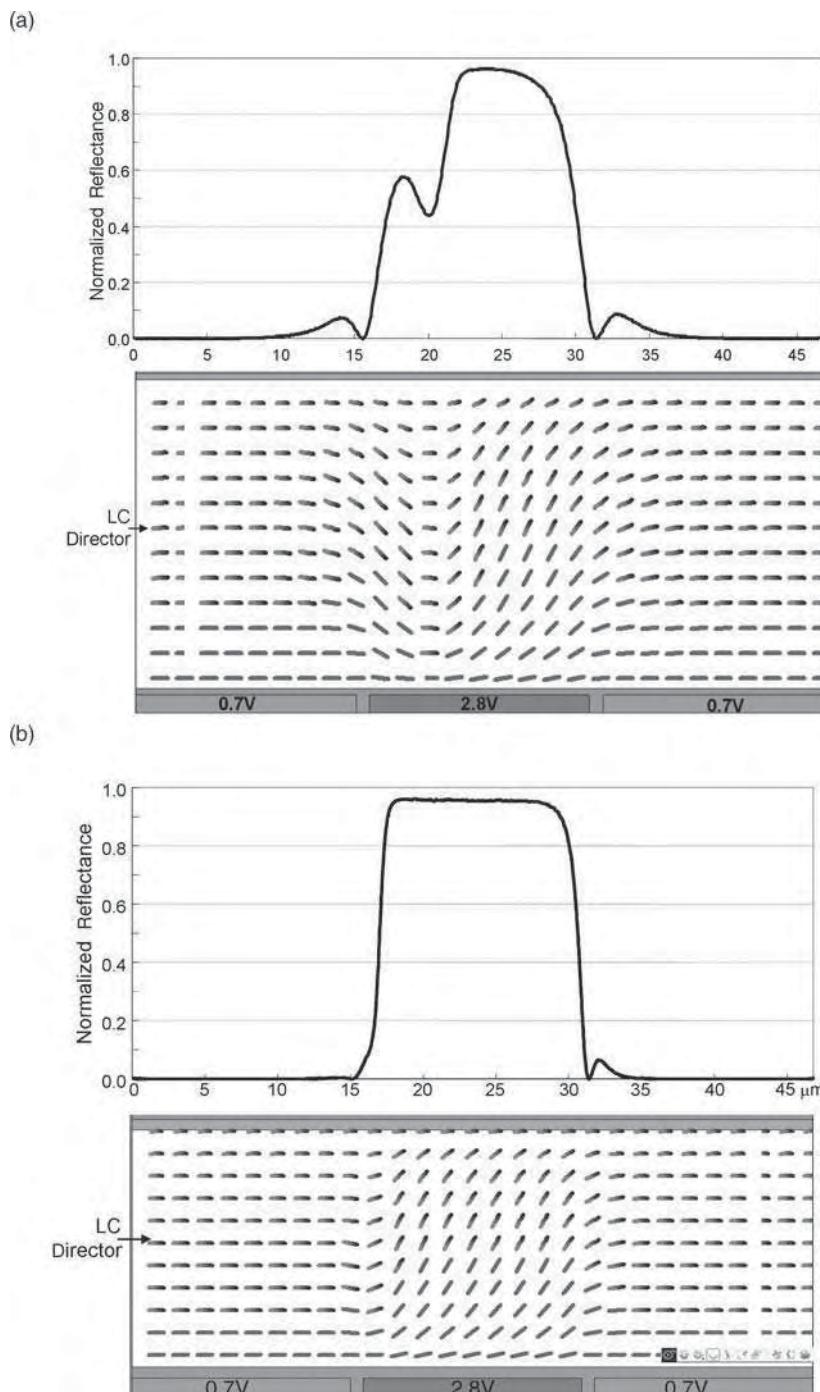

| 6.2.4     | Fringing Field Effect                            | 179        |

| 6.2.5     | Effect of Field Fringing on Image Quality        | 181        |

| 6.2.6     | Cell Gap                                         | 182        |

| 6.3       | Normally White Homogeneous Cell                  | 182        |

| 6.3.1     | Voltage-dependent Reflectance                    | 183        |

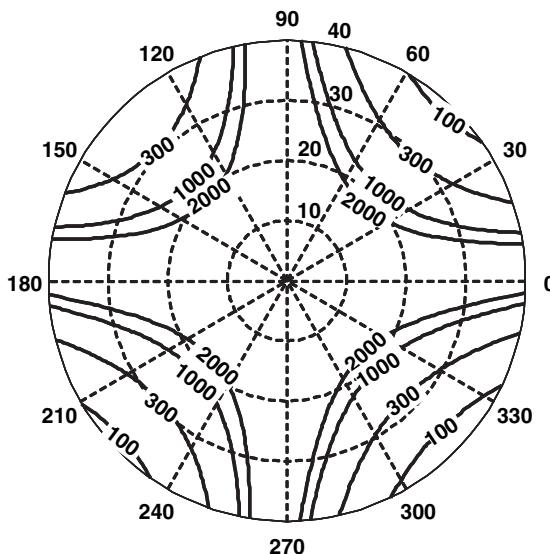

| 6.3.2     | Viewing Cone                                     | 183        |

| 6.3.3     | Fringing Field Effect                            | 184        |

| 6.4       | Reflective TN Cells                              | 184        |

| 6.5       | Normally White 90° MTN Cell                      | 186        |

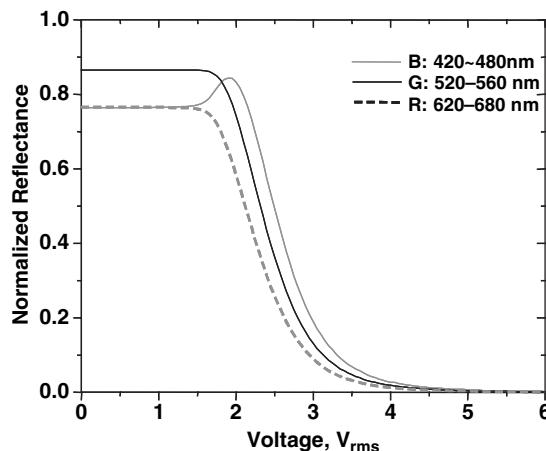

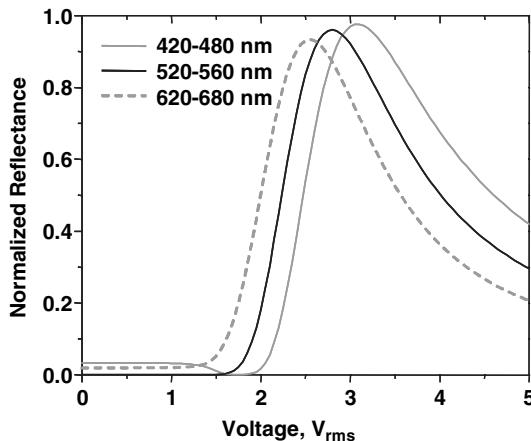

| 6.5.1     | Voltage-dependent Reflectance                    | 186        |

| 6.5.2     | Viewing Cone                                     | 187        |

| 6.5.3     | Fringing Field Effect                            | 187        |

| 6.6       | Normally White 63.6° MTN Cell                    | 189        |

| 6.6.1     | Voltage-dependent Reflectance                    | 189        |

| 6.6.2     | Viewing Cone                                     | 190        |

| 6.6.3     | Fringing Field Effect                            | 190        |

| 6.7       | Normally Black 63.6° TN Cell                     | 190        |

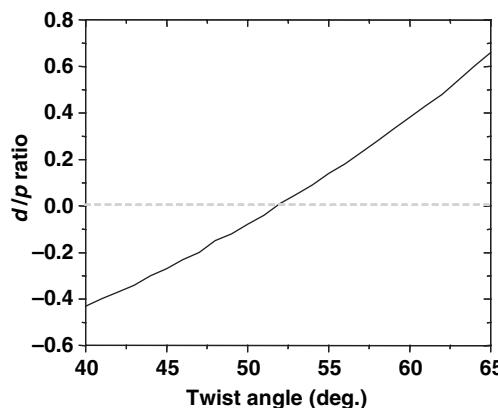

| 6.7.1     | Optimal <i>d/p</i> Ratio                         | 191        |

| 6.7.2     | Voltage-dependent Reflectance                    | 191        |

| 6.7.3     | Viewing Cone                                     | 192        |

| 6.7.4     | Fringing Field Effect                            | 193        |

|           |                                          |            |

|-----------|------------------------------------------|------------|

| 6.8       | Normally White 60° MTN Cell              | 194        |

| 6.8.1     | Bisector Effect                          | 195        |

| 6.8.2     | Viewing Cone                             | 196        |

| 6.9       | Normally White 45° MTN Cell              | 196        |

| 6.9.1     | Voltage-dependent Reflectance            | 197        |

| 6.9.2     | Viewing Cone                             | 197        |

| 6.9.3     | Fringing Field Effect                    | 199        |

| 6.10      | Normally Black 45° TN                    | 199        |

| 6.10.1    | Voltage-dependent Reflectance            | 200        |

| 6.10.2    | Viewing Cone                             | 200        |

| 6.10.3    | Fringing Field Effect                    | 200        |

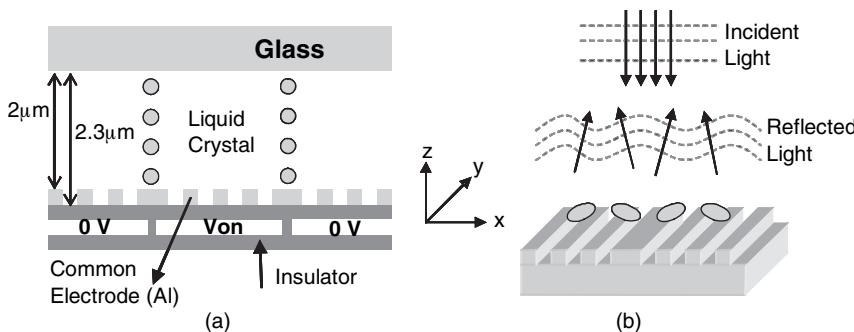

| 6.11      | Finger-on-Plane Structure                | 201        |

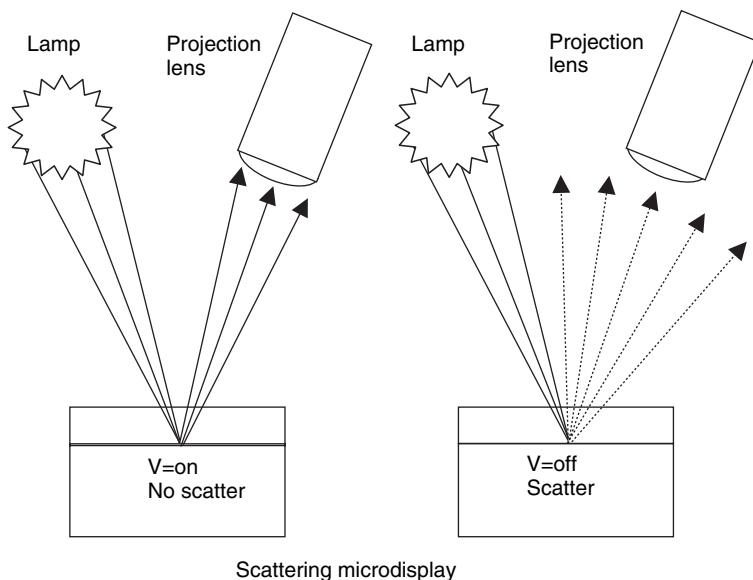

| 6.12      | Scattering and Diffractive Microdisplays | 203        |

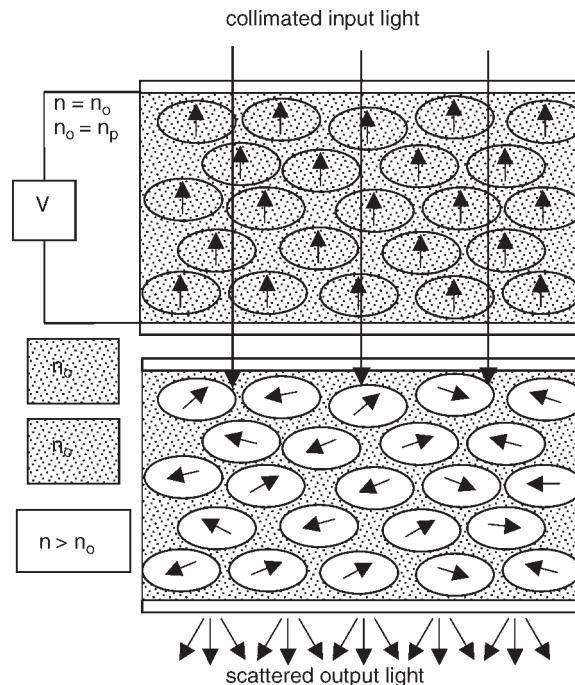

| 6.12.1    | Polymer Dispersed Nematics               | 203        |

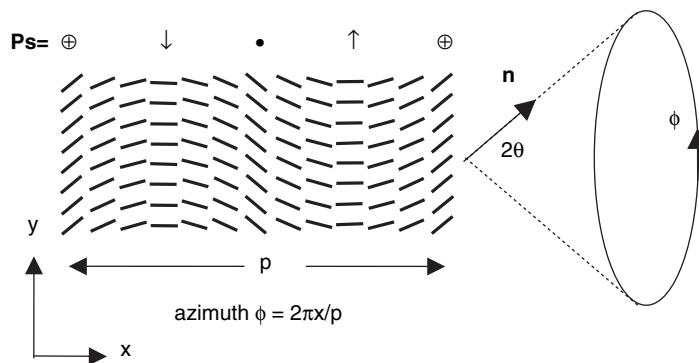

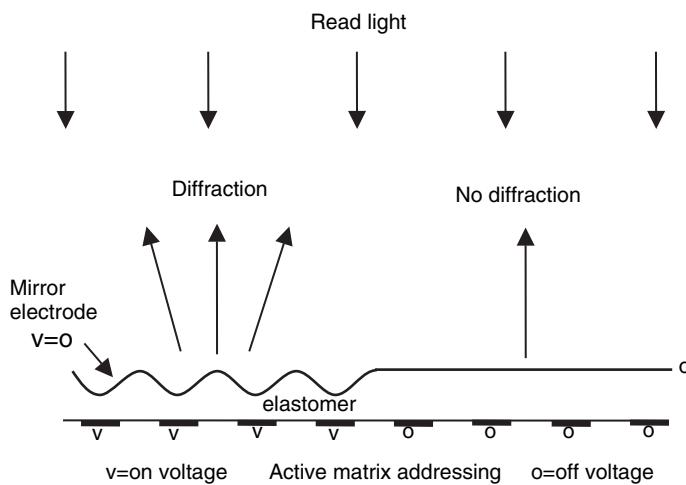

| 6.12.2    | Diffraction                              | 205        |

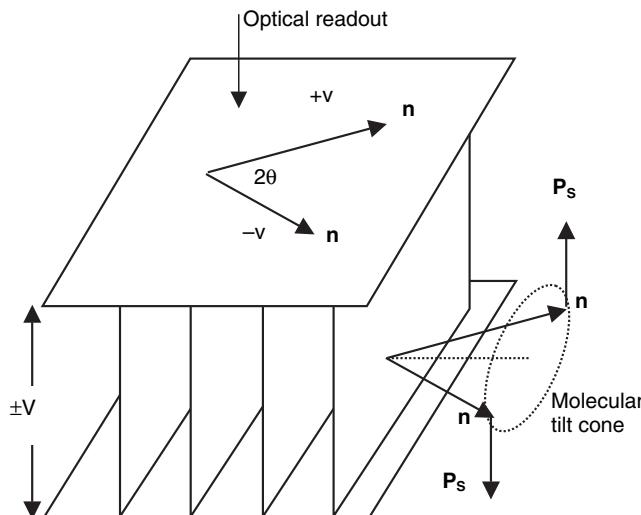

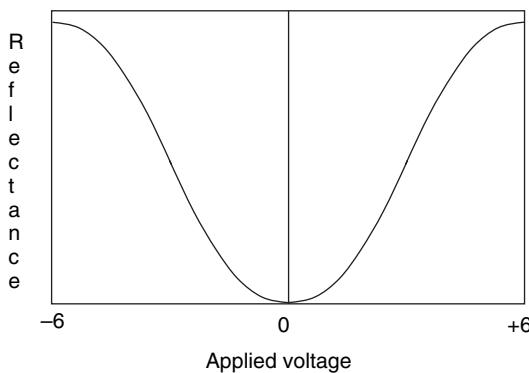

| 6.13      | Ferroelectric Liquid Crystals            | 205        |

| 6.13.1    | Surface-Stabilized FLC                   | 206        |

| 6.13.2    | Other FLC Modes                          | 207        |

| 6.14      | References                               | 208        |

| <b>7.</b> | <b>LCD Assembly and Testing</b>          | <b>211</b> |

| 7.1       | Background                               | 211        |

| 7.2       | Back-end Processing                      | 212        |

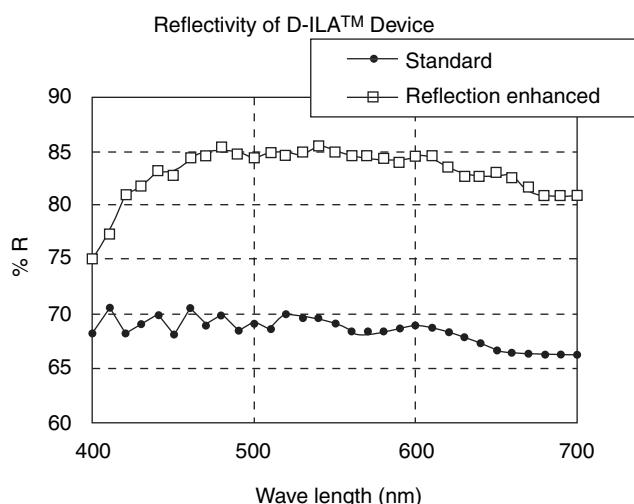

| 7.2.1     | Dielectric Mirror                        | 213        |

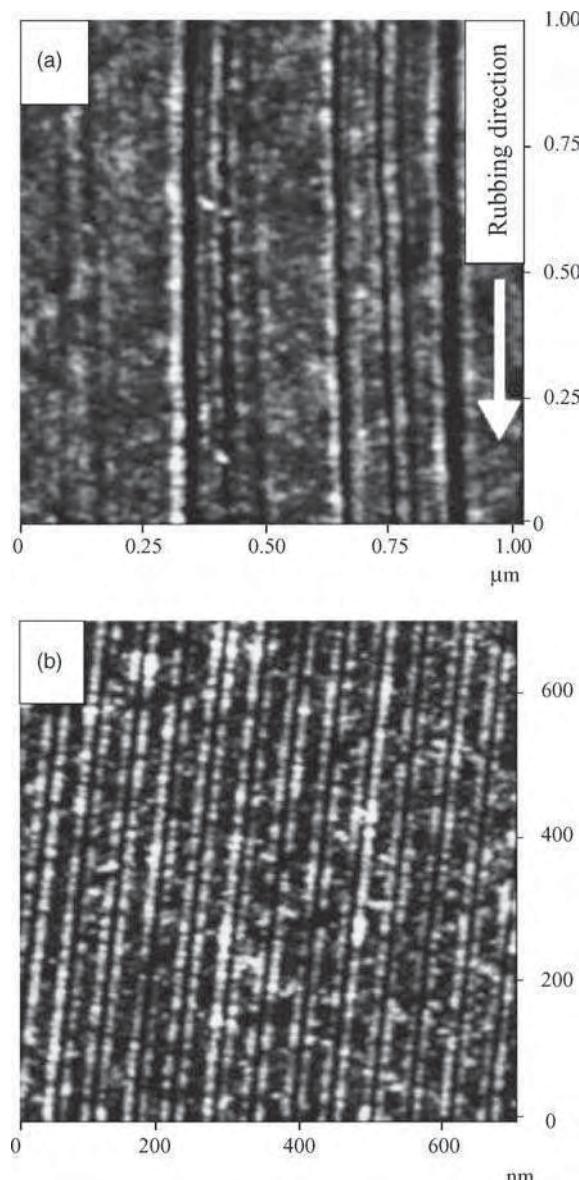

| 7.2.2     | Liquid Crystal Alignment Layer           | 214        |

| 7.3       | Assembly Components                      | 214        |

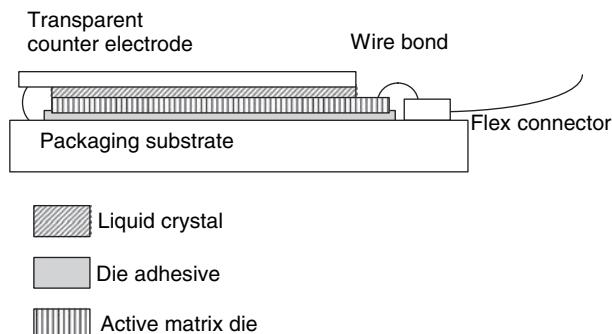

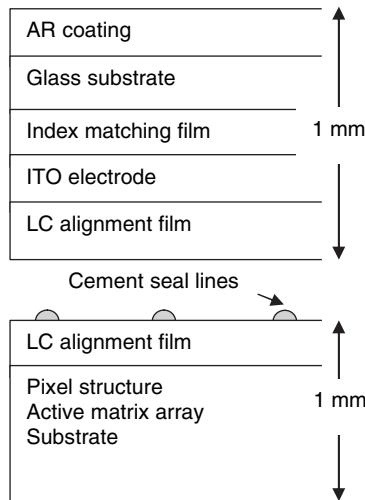

| 7.3.1     | Active Matrix Substrate                  | 215        |

| 7.3.2     | Transparent Counter-Electrode            | 216        |

| 7.3.3     | Cell Gap Spacers                         | 216        |

| 7.3.4     | Liquid Crystal Seal                      | 217        |

| 7.3.5     | Liquid Crystal                           | 218        |

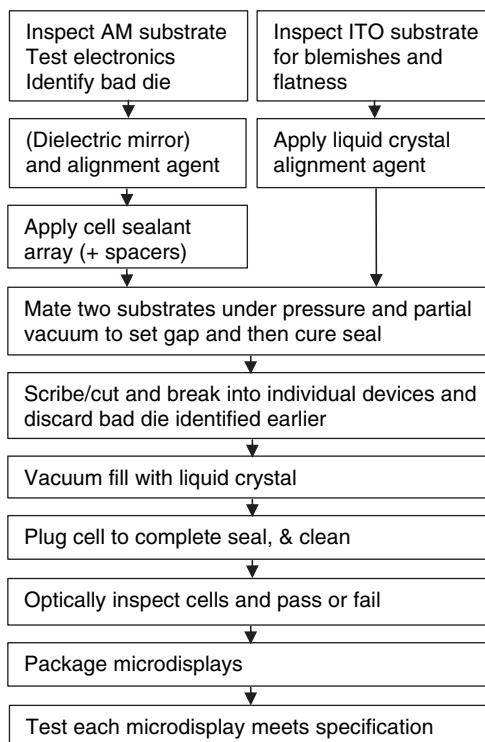

| 7.4       | Assembly Methods                         | 219        |

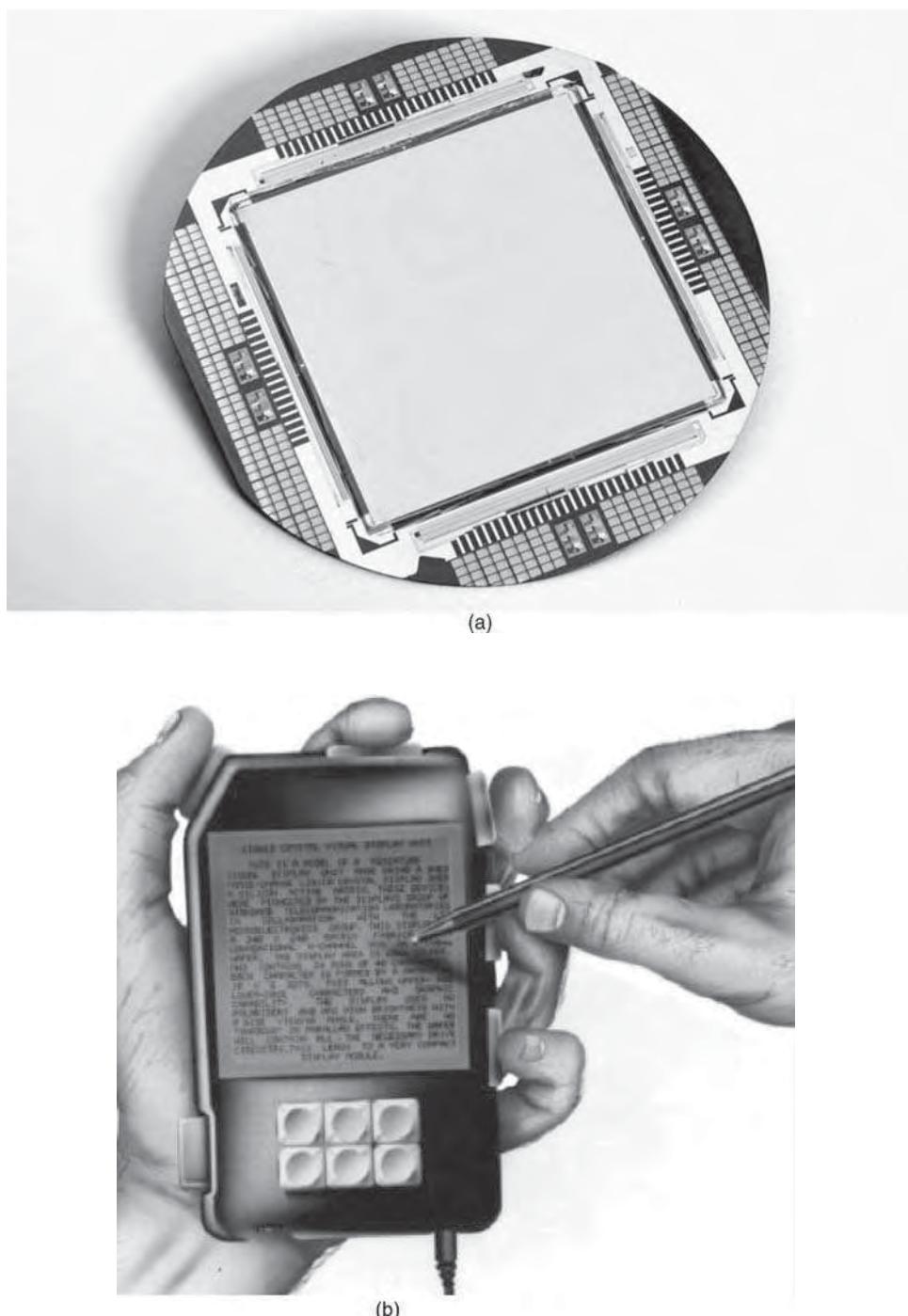

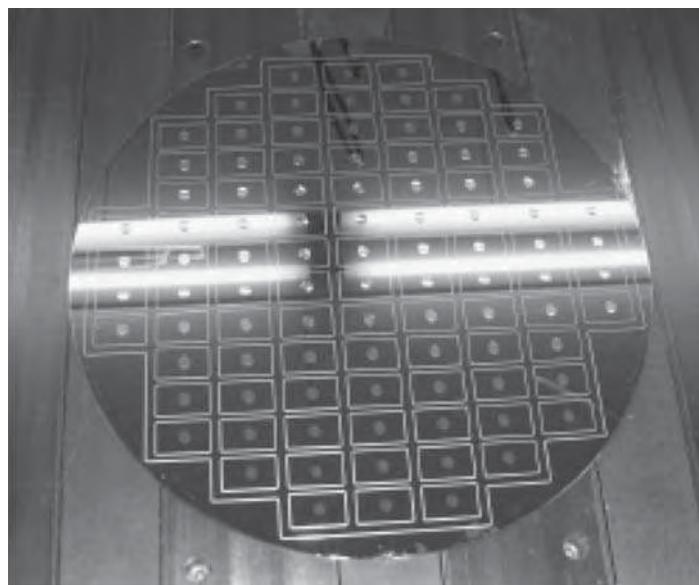

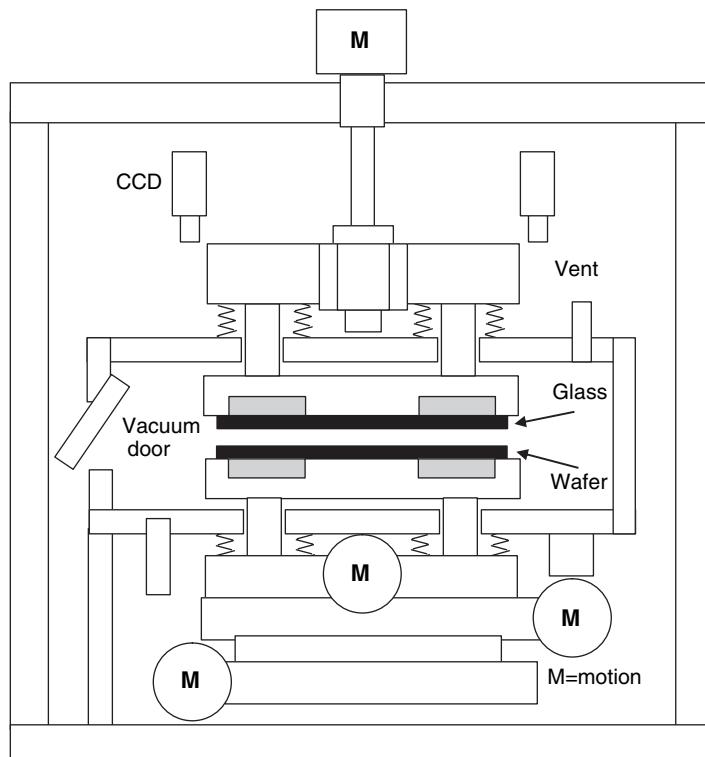

| 7.4.1     | Wafer-Scale Assembly                     | 219        |

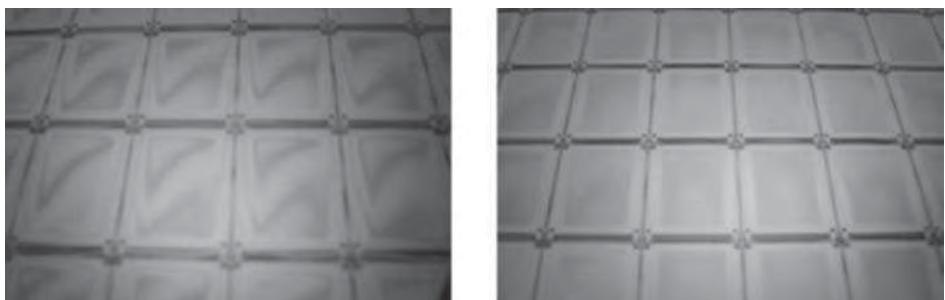

| 7.4.2     | Seal and Spacer Application              | 220        |

| 7.4.3     | Assembly Pressure                        | 220        |

| 7.4.4     | Singulation                              | 220        |

| 7.4.5     | Cell Filling and Plug                    | 220        |

| 7.4.6     | One-Drop Filling                         | 221        |

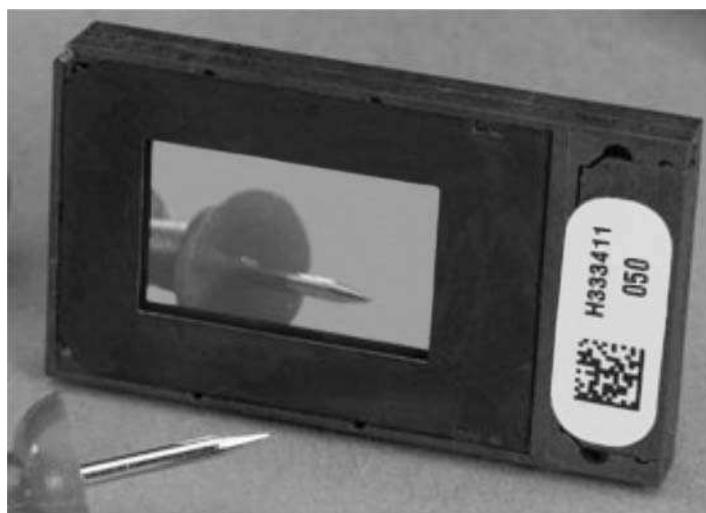

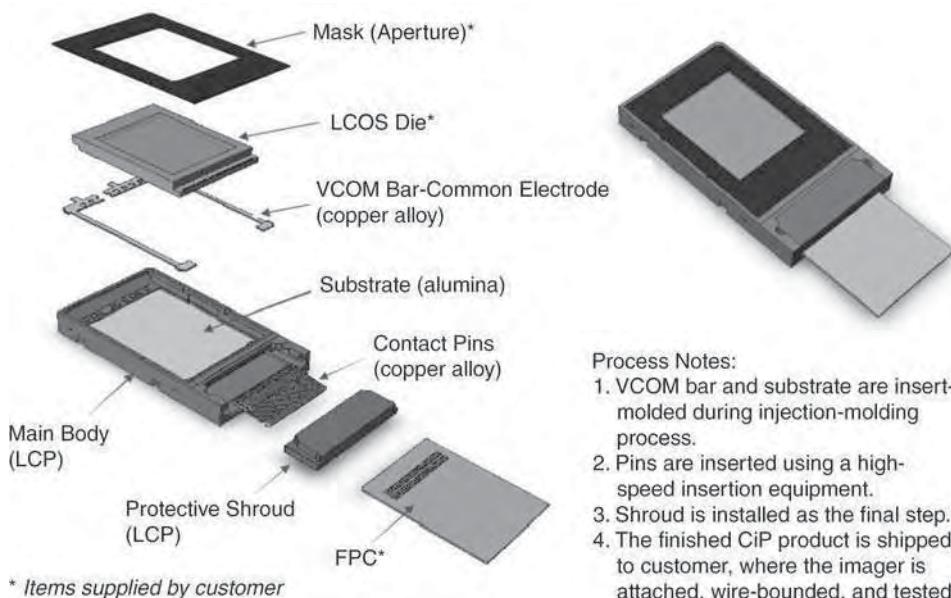

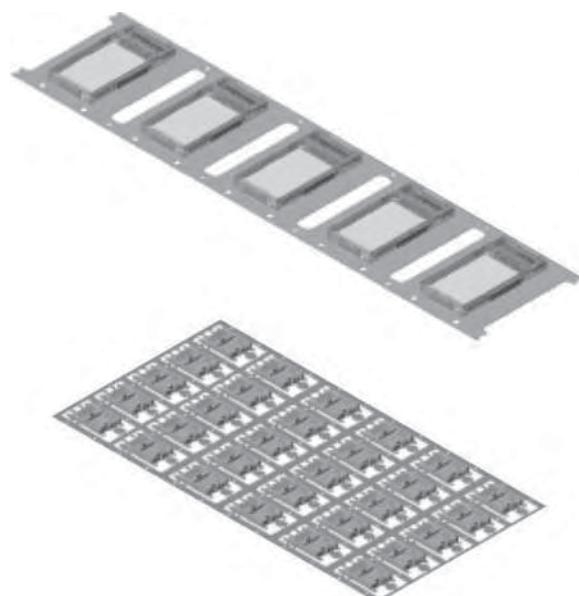

| 7.4.7     | Packaging                                | 223        |

| 7.5       | Testing                                  | 225        |

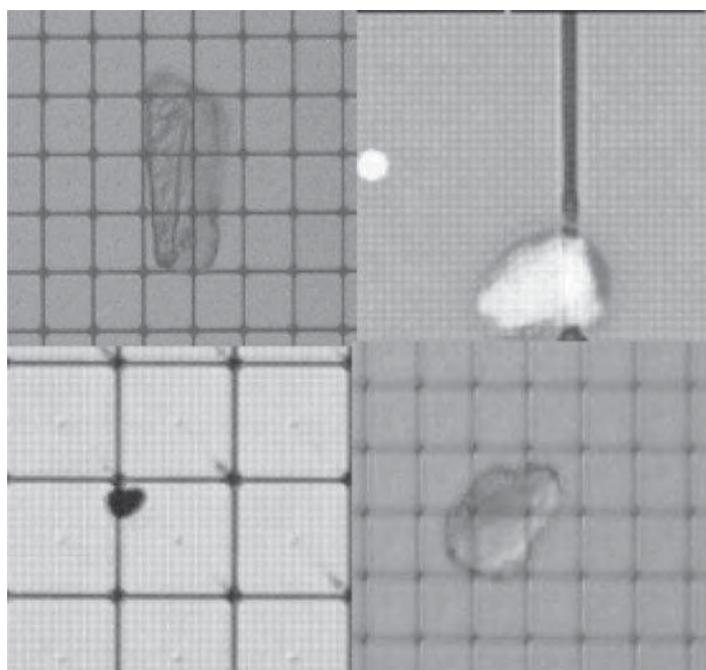

| 7.5.1     | Assembly Tests                           | 225        |

| 7.5.2     | Specifications                           | 226        |

| 7.5.3     | Specification Tests                      | 227        |

| 7.5.4     | Stress Tests                             | 227        |

| 7.6       | References                               | 229        |

| <b>8.</b> | <b>Micromechanical Devices</b>           | <b>231</b> |

| 8.1       | Background                               | 231        |

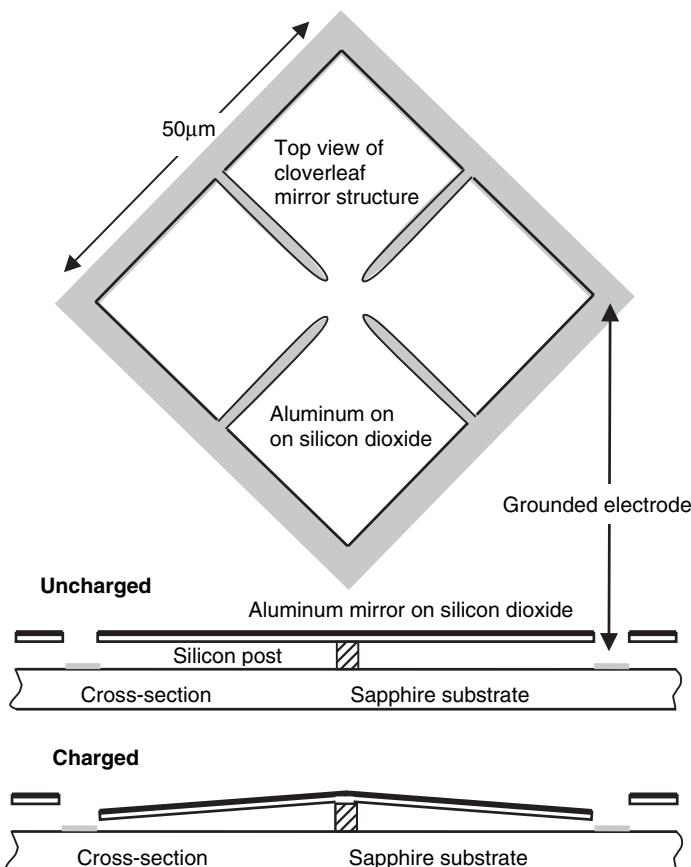

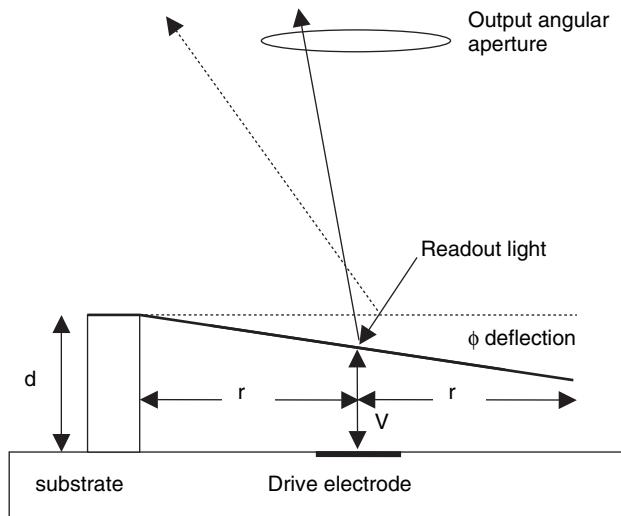

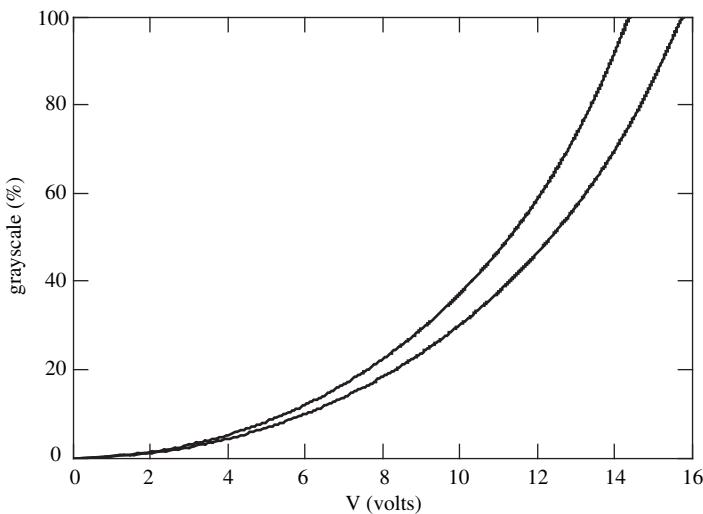

| 8.1.1     | Electrostatic Deflection                 | 233        |

| 8.2       | Digital Mirror Device                    | 235        |

| 8.2.1     | Background                               | 235        |

|           |                                                 |            |

|-----------|-------------------------------------------------|------------|

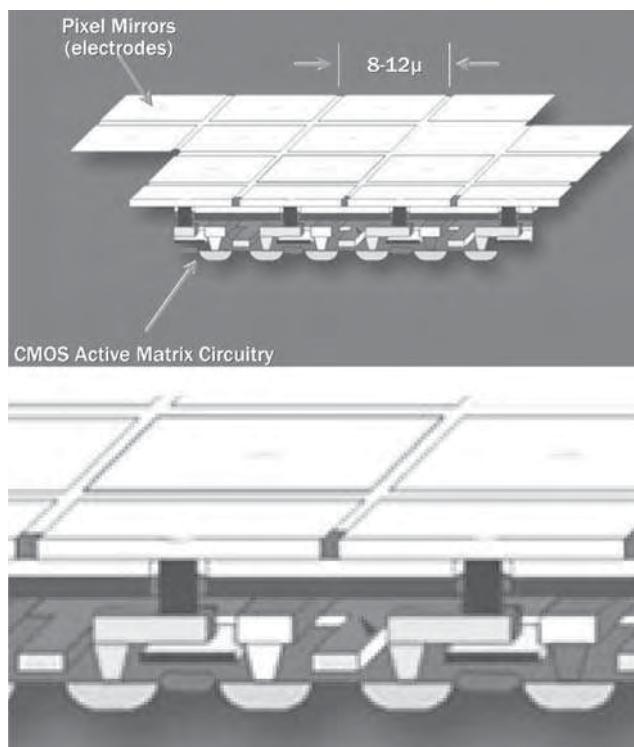

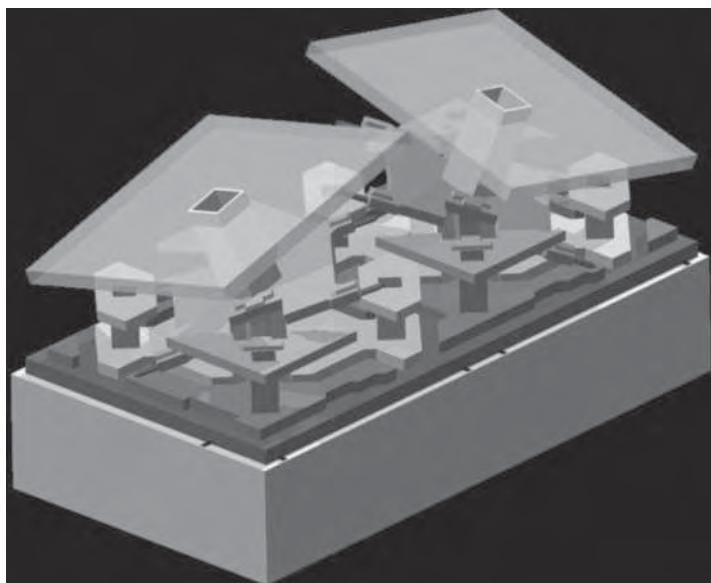

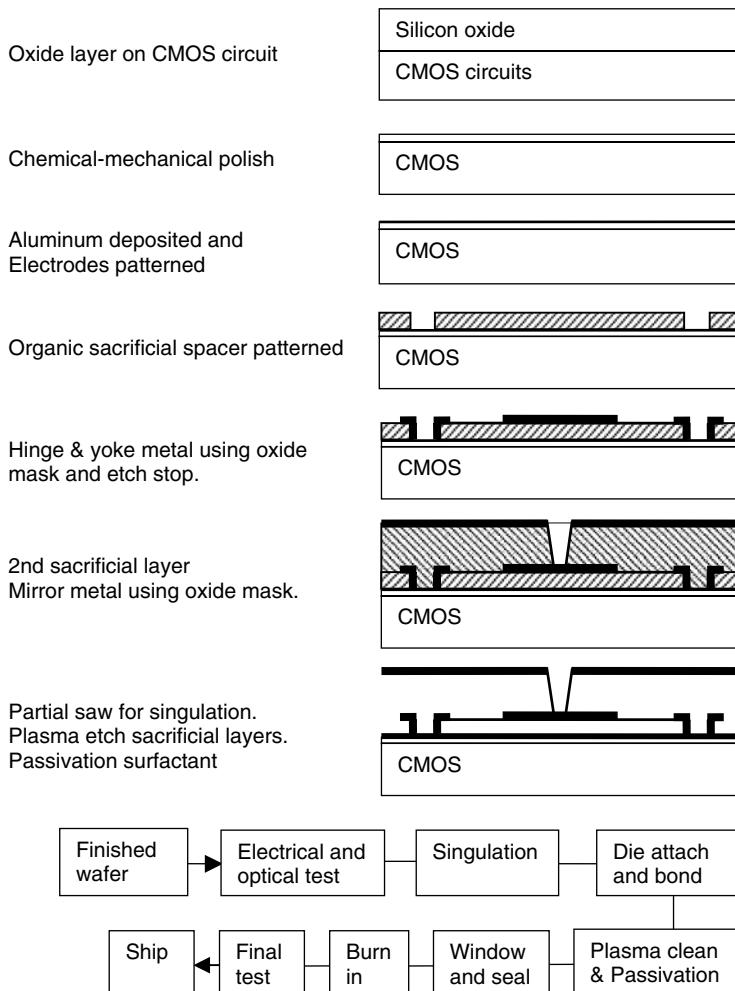

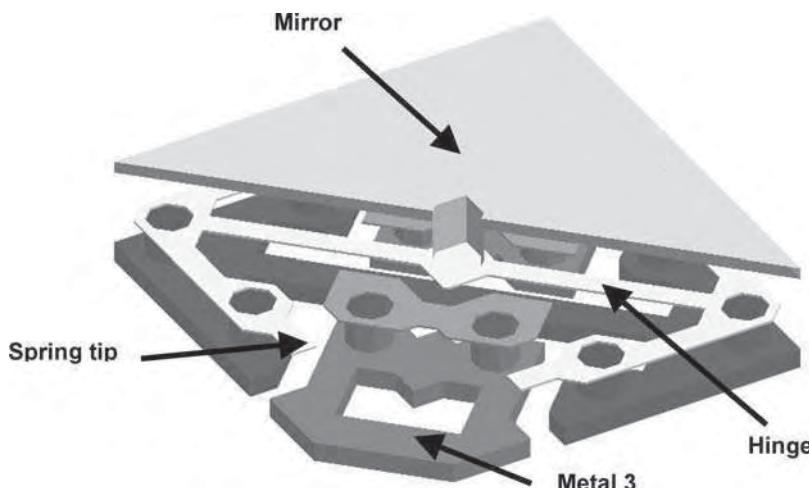

| 8.2.2     | Structure                                       | 236        |

| 8.2.3     | Fabrication                                     | 239        |

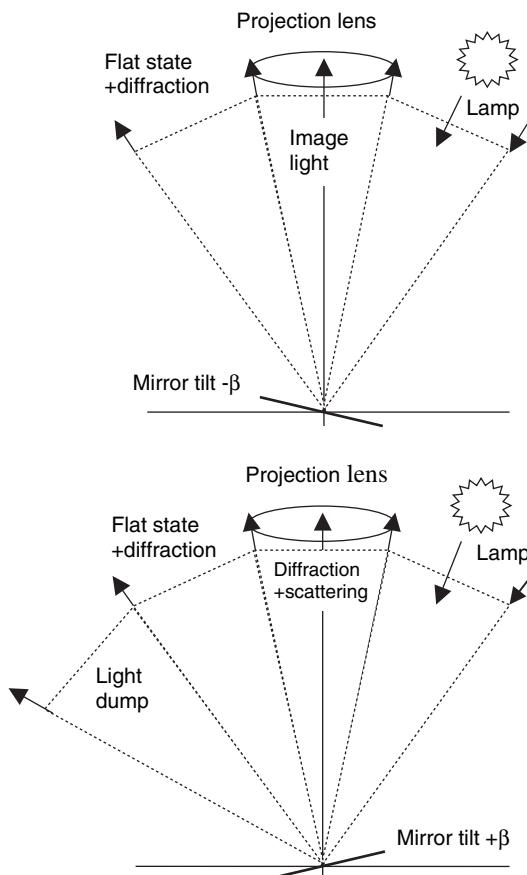

| 8.2.4     | Operation and Throughput Efficiency             | 241        |

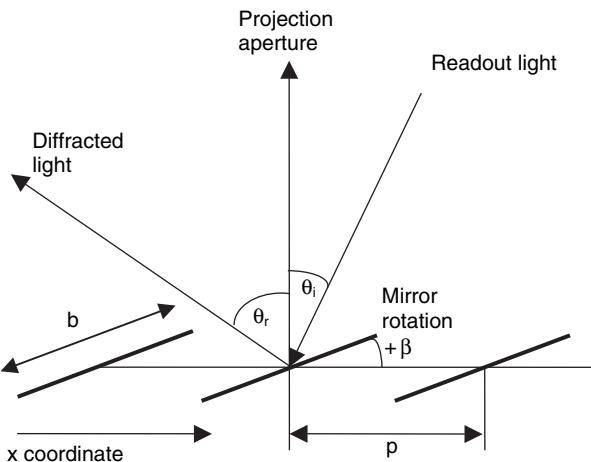

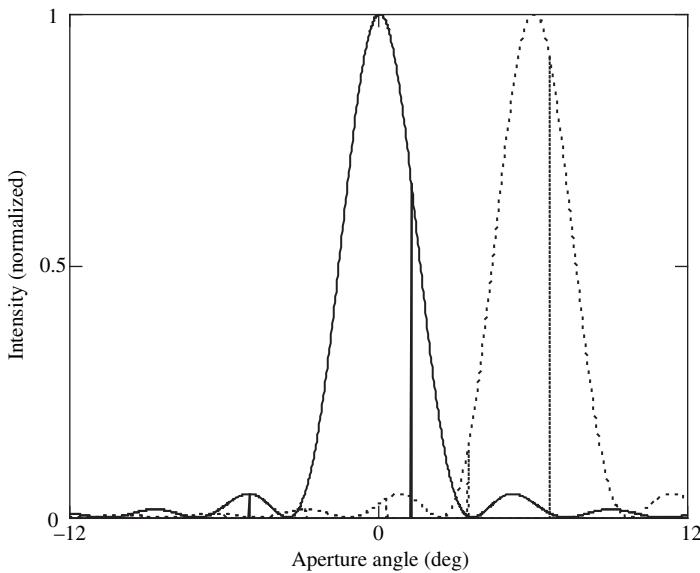

| 8.2.5     | Diffraction Efficiency and Contrast Ratio       | 242        |

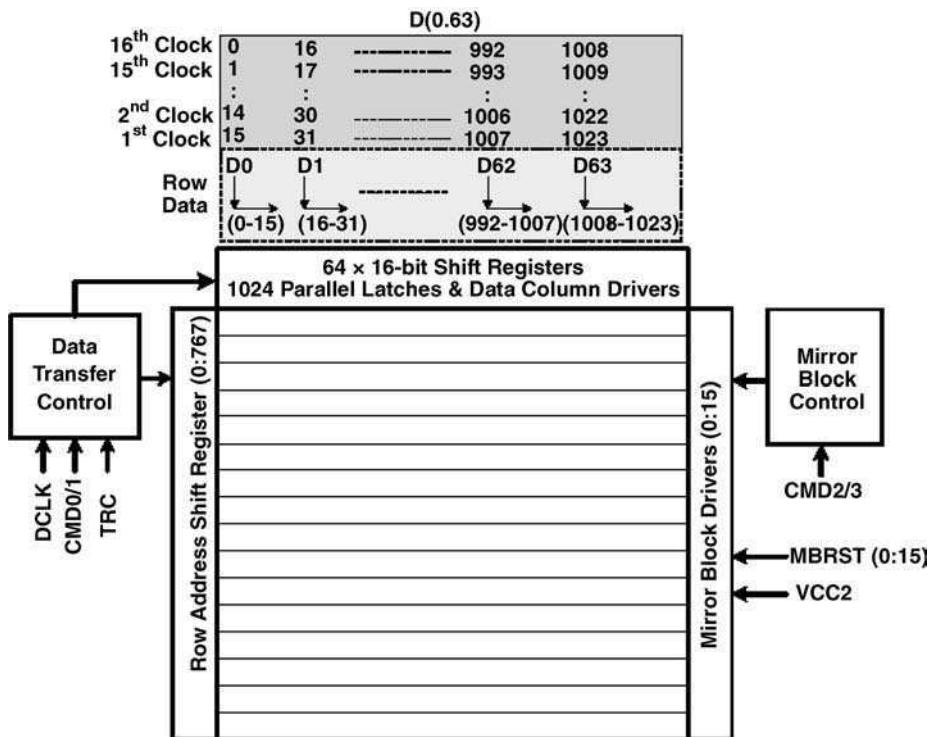

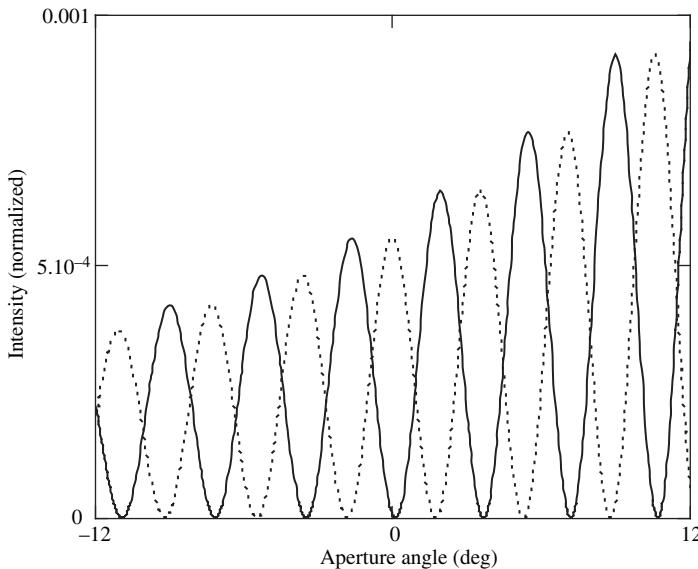

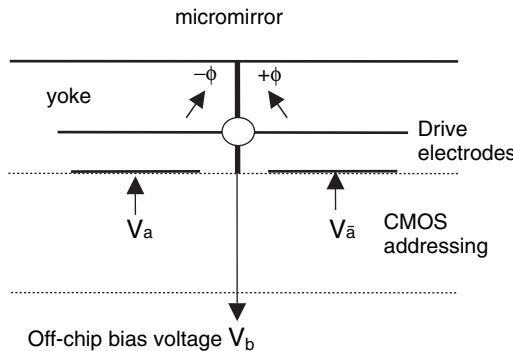

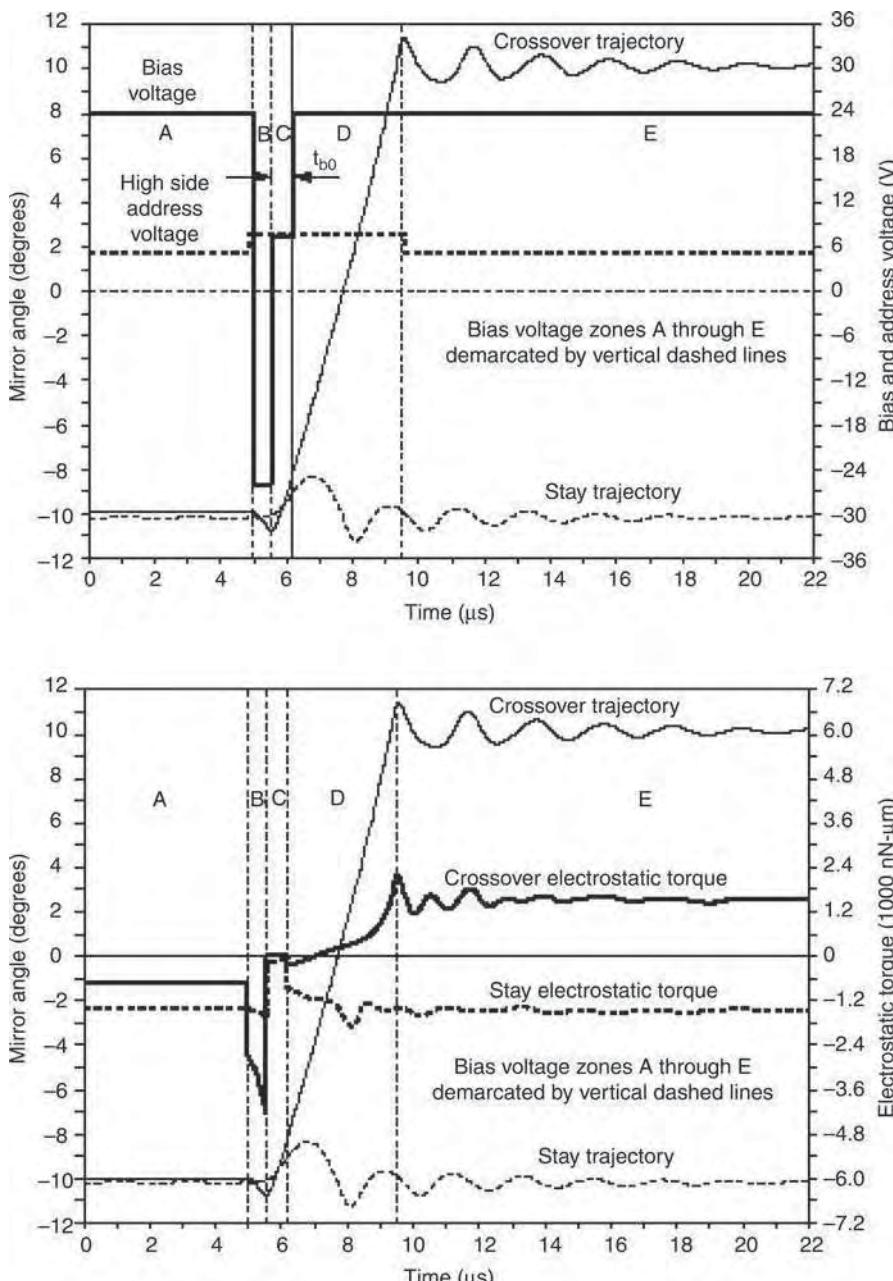

| 8.2.6     | Addressing                                      | 246        |

| 8.2.7     | Lifetime                                        | 250        |

| 8.2.8     | Fast-Track Pixel Design                         | 251        |

| 8.3       | Piezoelectric Micromirror                       | 252        |

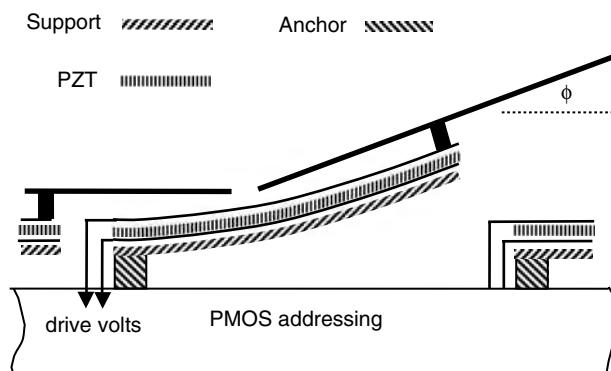

| 8.3.1     | Structure and Operation                         | 252        |

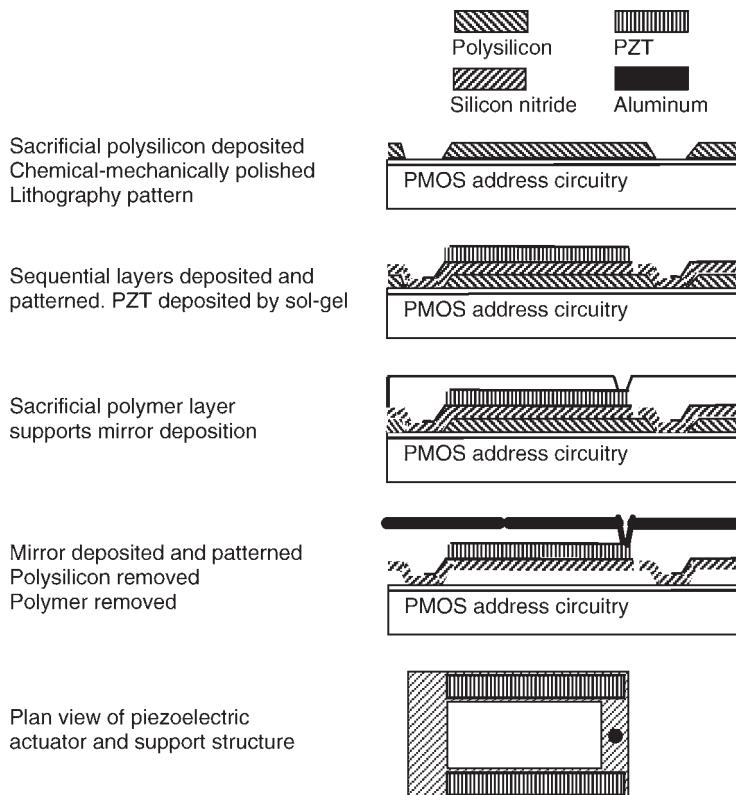

| 8.3.2     | Fabrication                                     | 253        |

| 8.4       | Grating Light Valve                             | 254        |

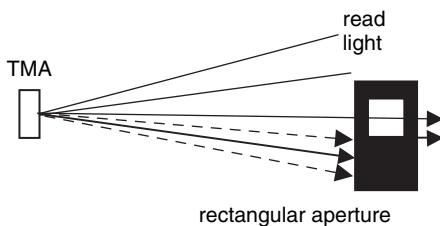

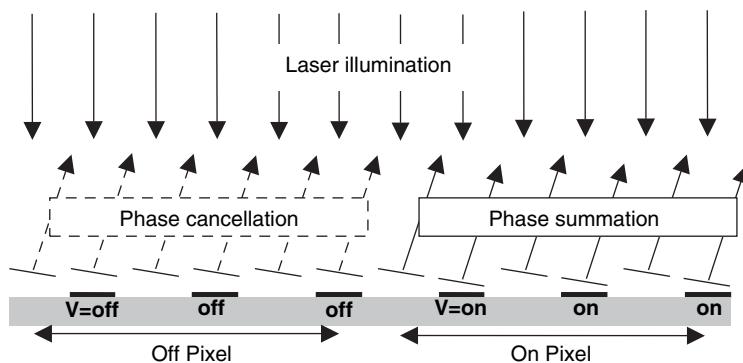

| 8.4.1     | Operation and Performance                       | 254        |

| 8.4.2     | Fabrication and Testing                         | 257        |

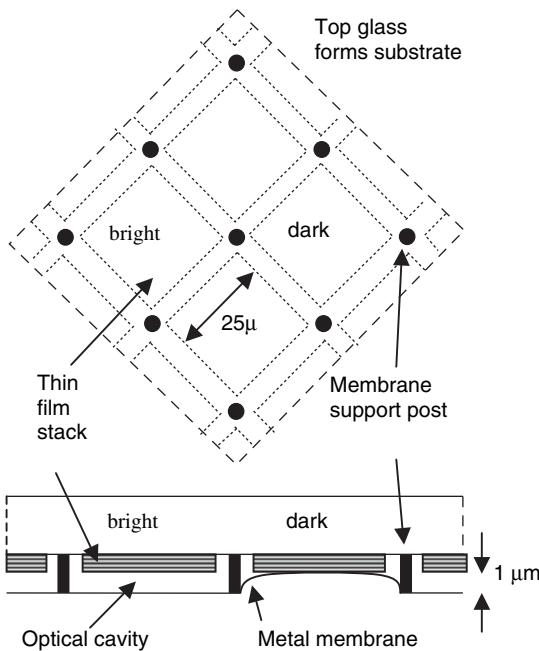

| 8.5       | Interference Modulation                         | 258        |

| 8.6       | Further Development                             | 259        |

| 8.7       | References                                      | 260        |

| <b>9.</b> | <b>Emissive Microdisplays</b>                   | <b>263</b> |

| 9.1       | Introduction                                    | 263        |

| 9.1.1     | Background to Organic Electronics and Displays  | 263        |

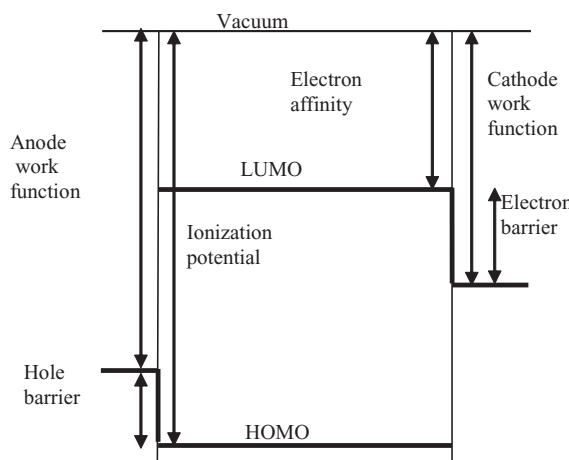

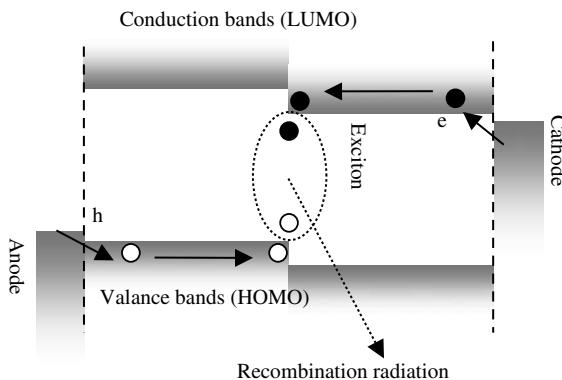

| 9.1.2     | Basic Operation                                 | 264        |

| 9.2       | Organic Emissive Materials                      | 268        |

| 9.2.1     | Classification                                  | 268        |

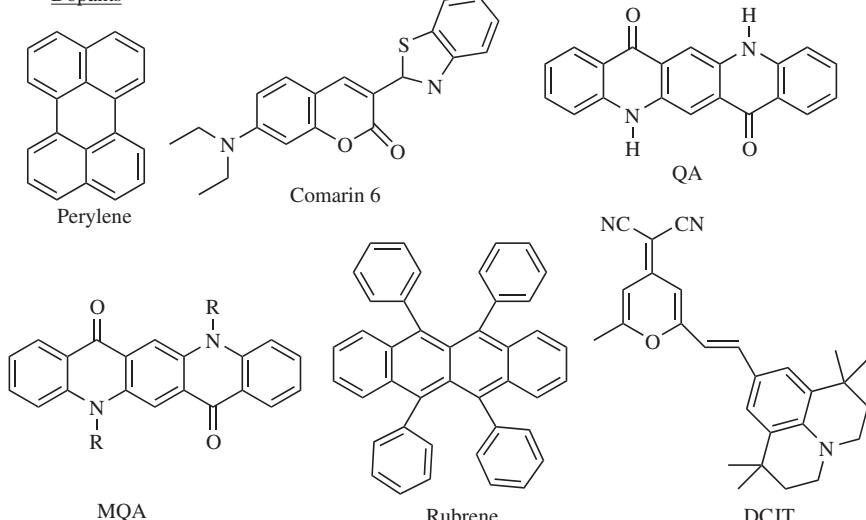

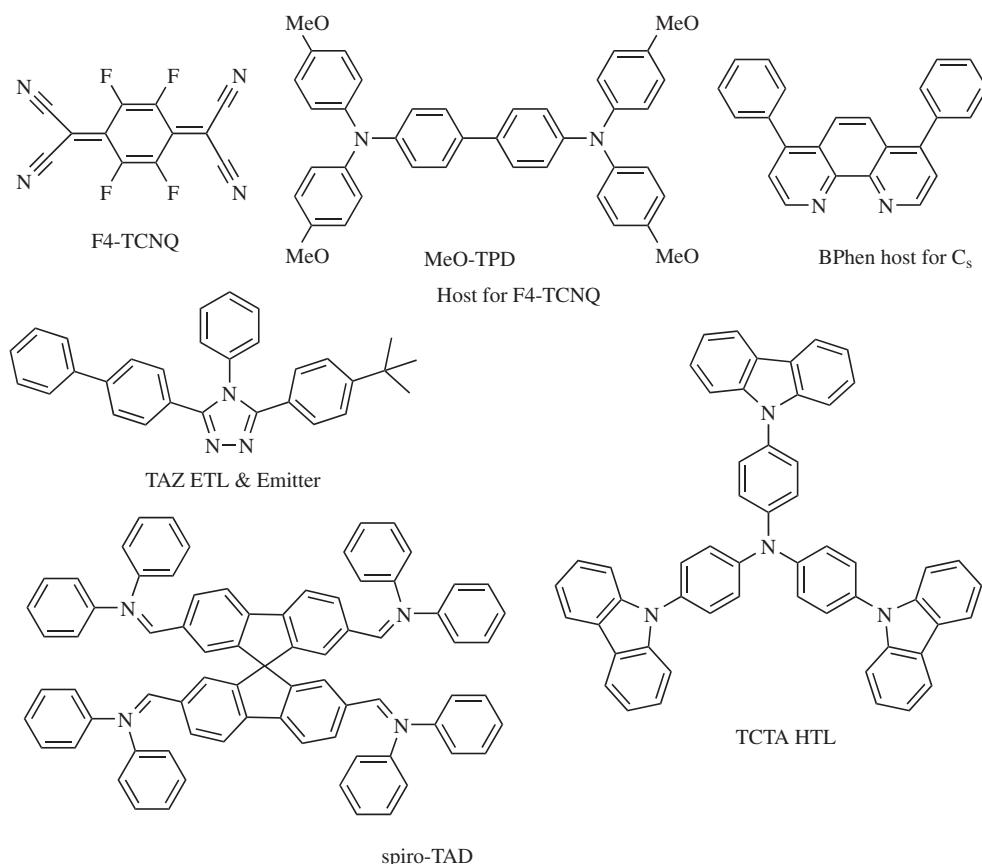

| 9.2.2     | Small-Molecule Materials                        | 269        |

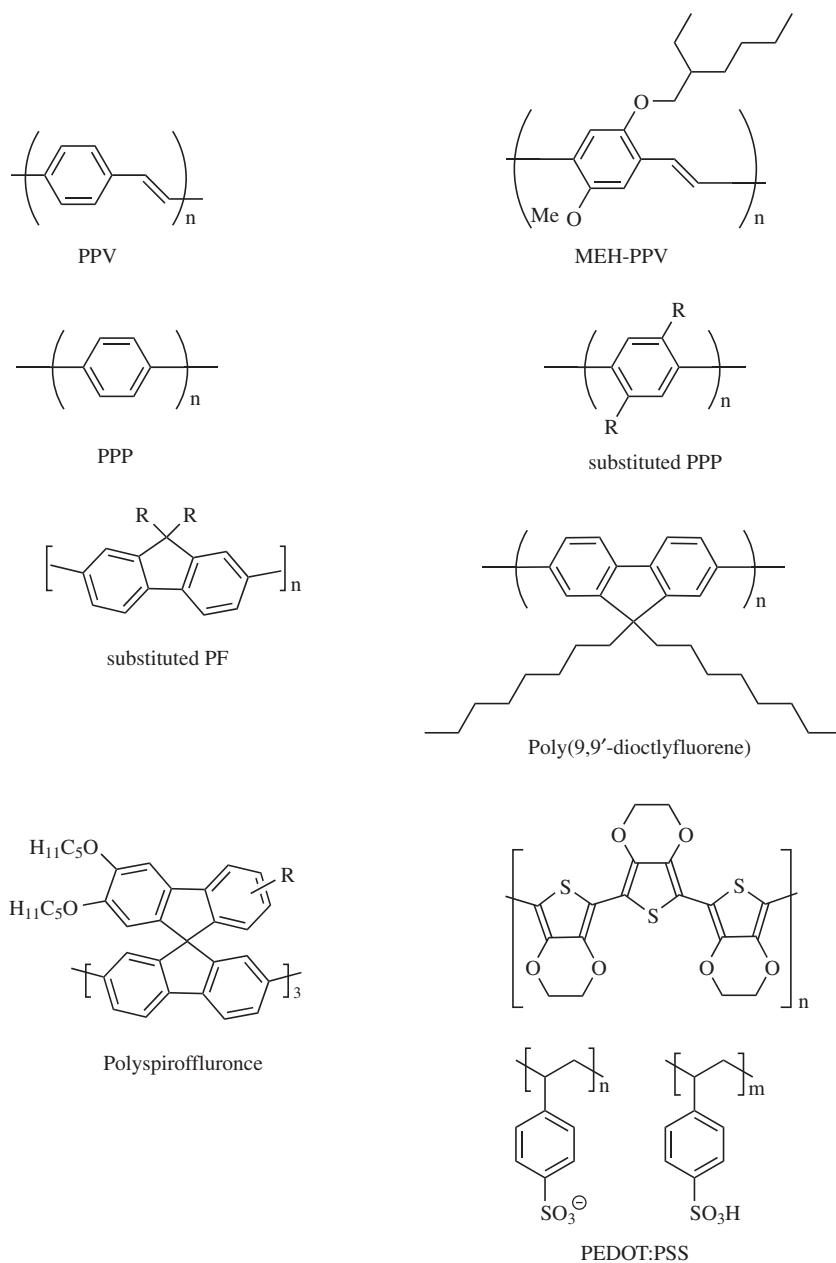

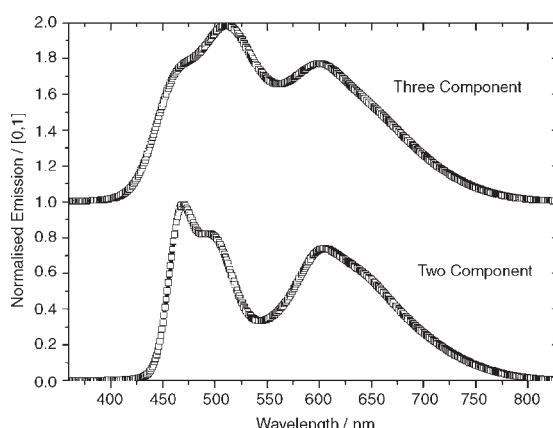

| 9.2.3     | Polymer Materials                               | 271        |

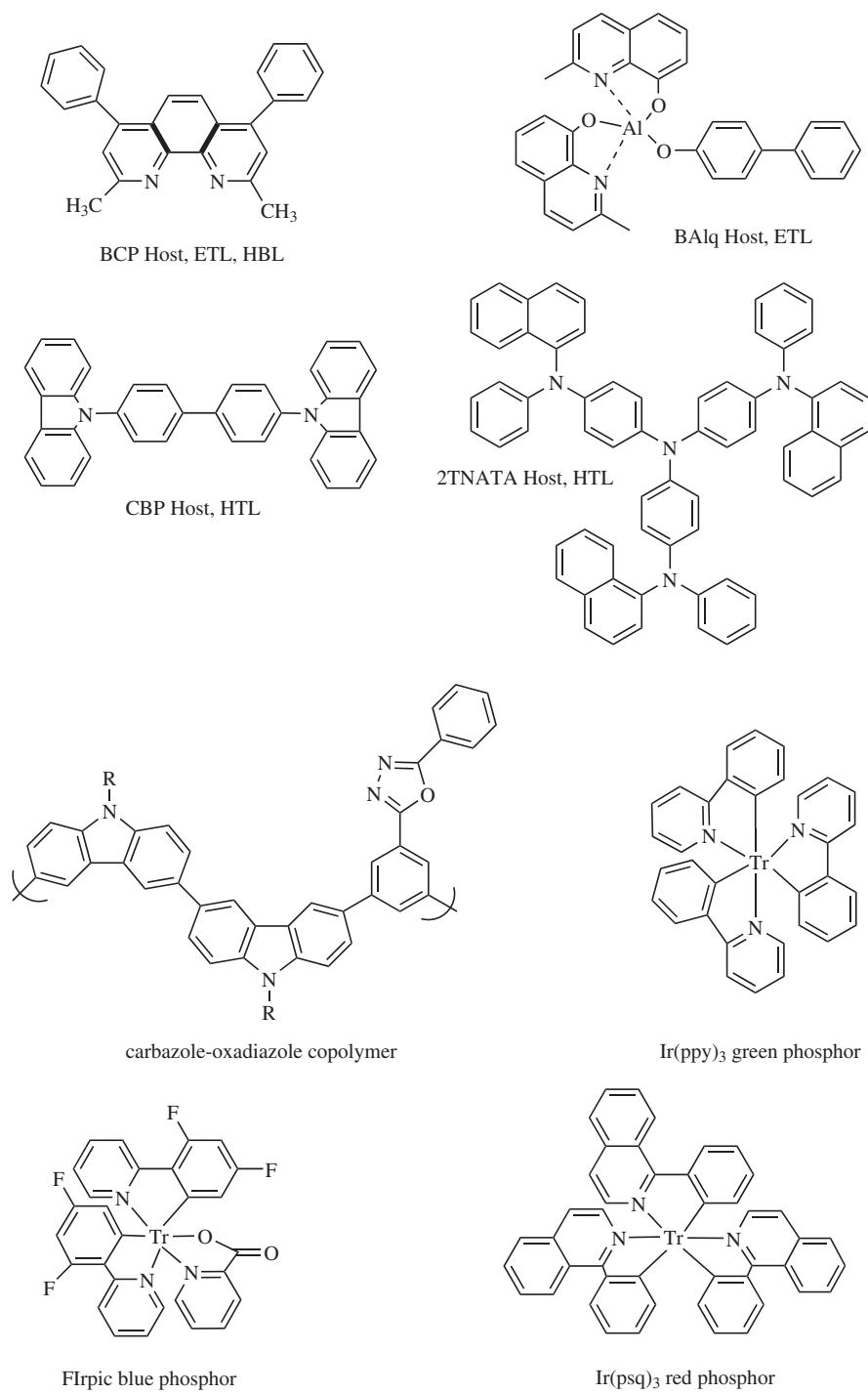

| 9.2.4     | Phosphorescent OLED                             | 273        |

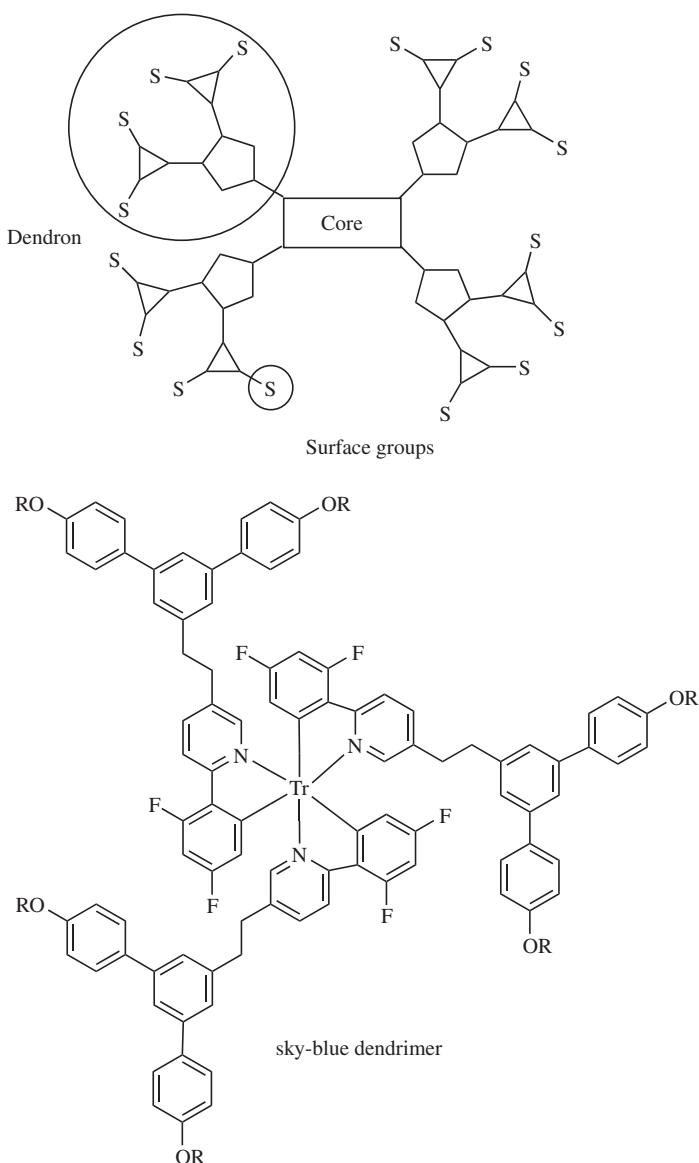

| 9.2.5     | Dendrimers                                      | 273        |

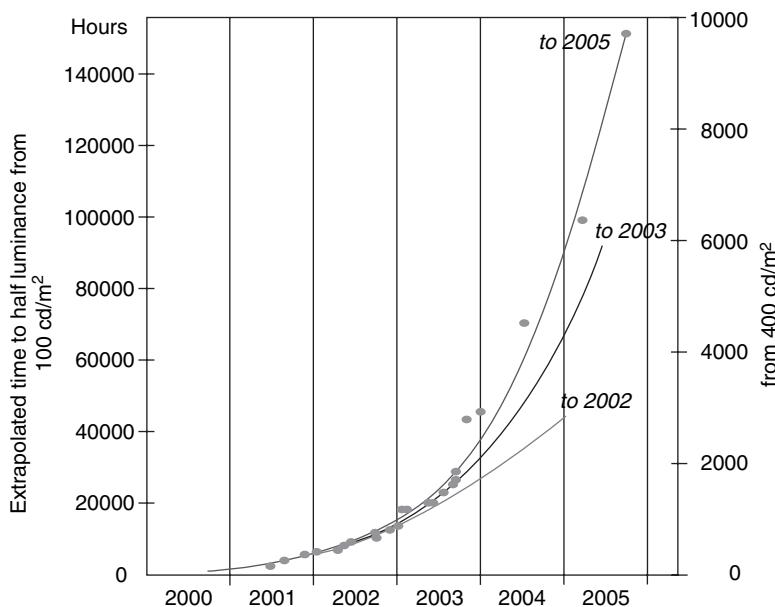

| 9.2.6     | Example Performance Data                        | 273        |

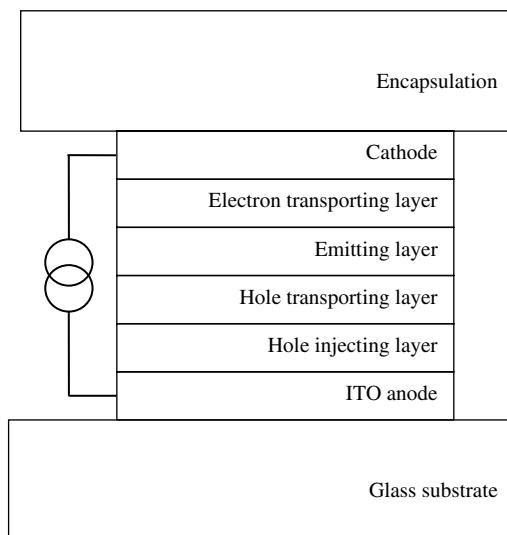

| 9.3       | Device Construction and Manufacture             | 277        |

| 9.3.1     | SMOLED                                          | 278        |

| 9.3.2     | PHOLED                                          | 279        |

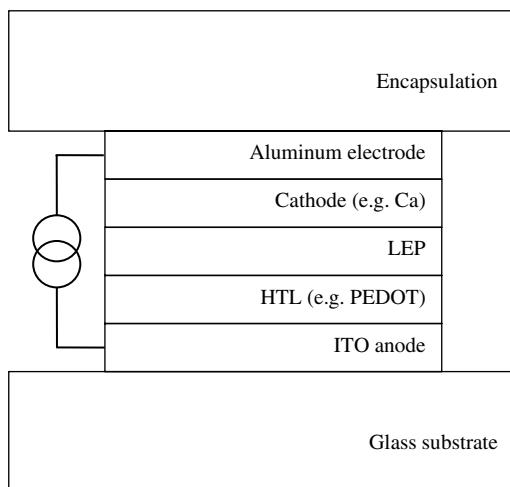

| 9.3.3     | P-OLED                                          | 279        |

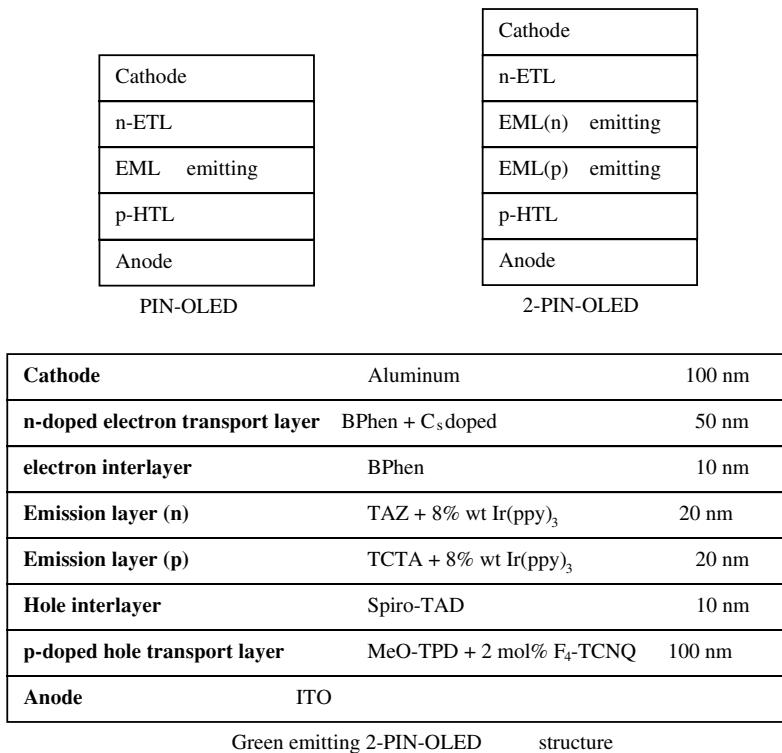

| 9.3.4     | PIN OLED                                        | 279        |

| 9.3.5     | Encapsulation and Packaging                     | 280        |

| 9.3.6     | Display Efficiency                              | 281        |

| 9.4       | Device Characteristics                          | 282        |

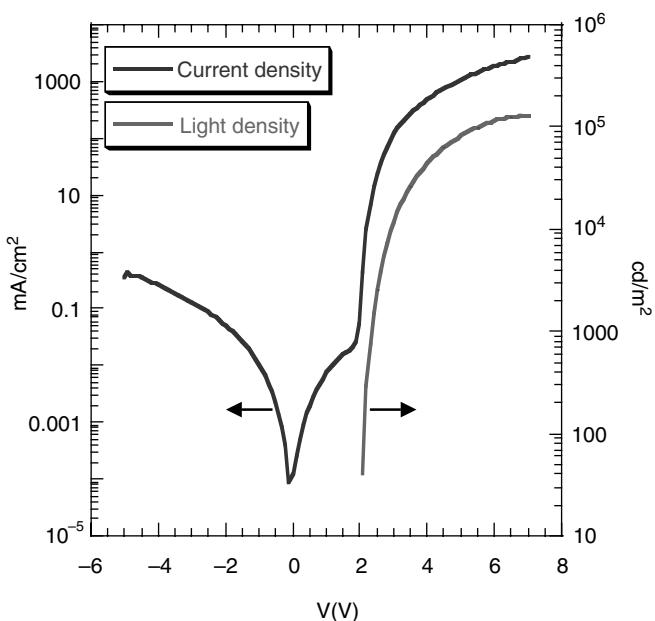

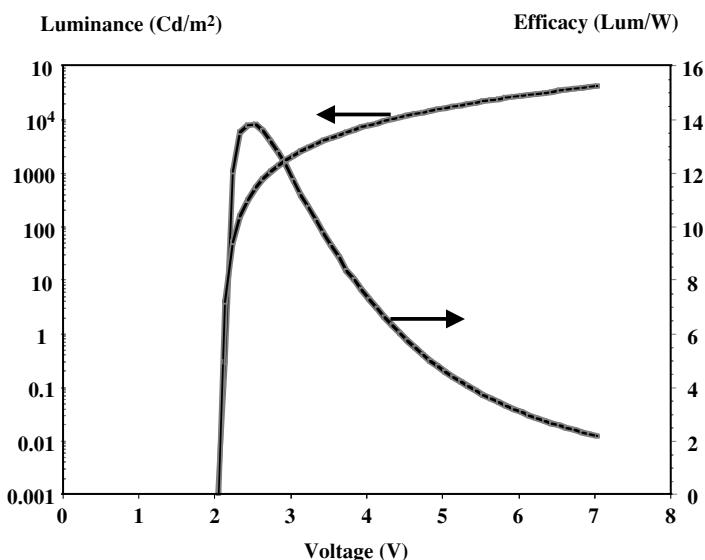

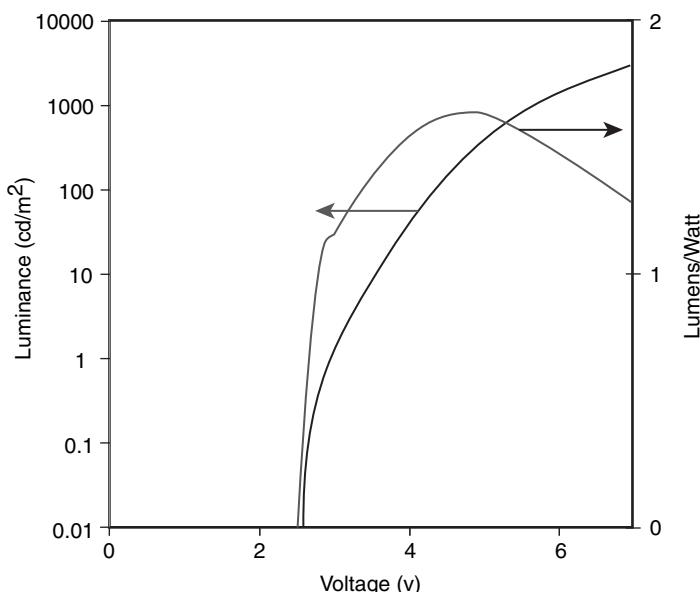

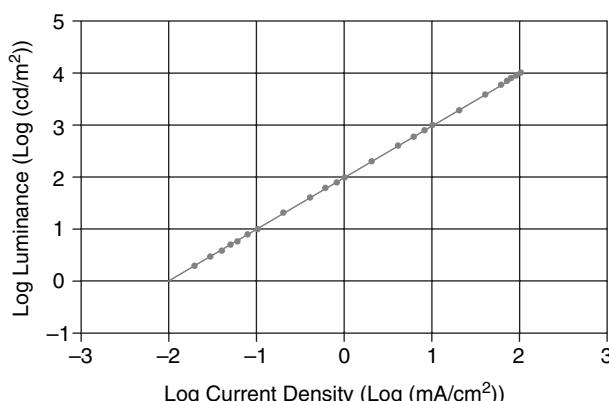

| 9.4.1     | DC Characteristics                              | 282        |

| 9.4.2     | Switching Time                                  | 284        |

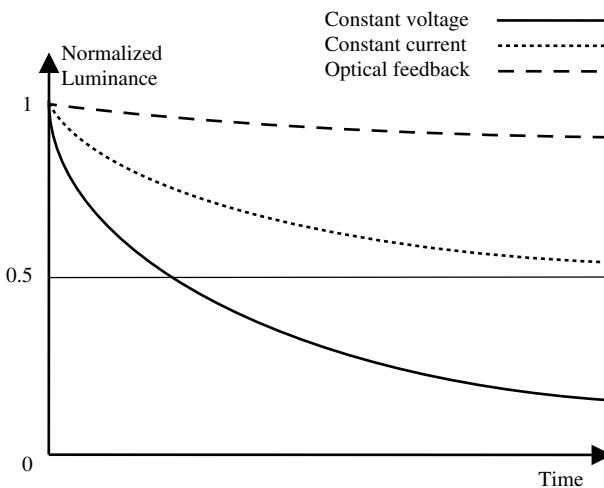

| 9.4.3     | Aging                                           | 285        |

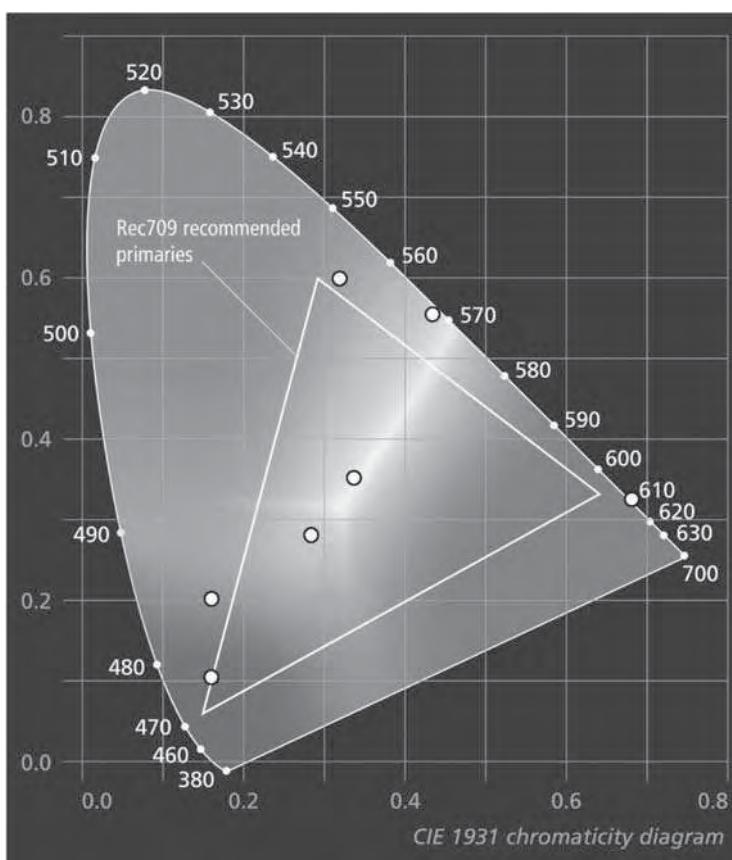

| 9.5       | Color                                           | 286        |

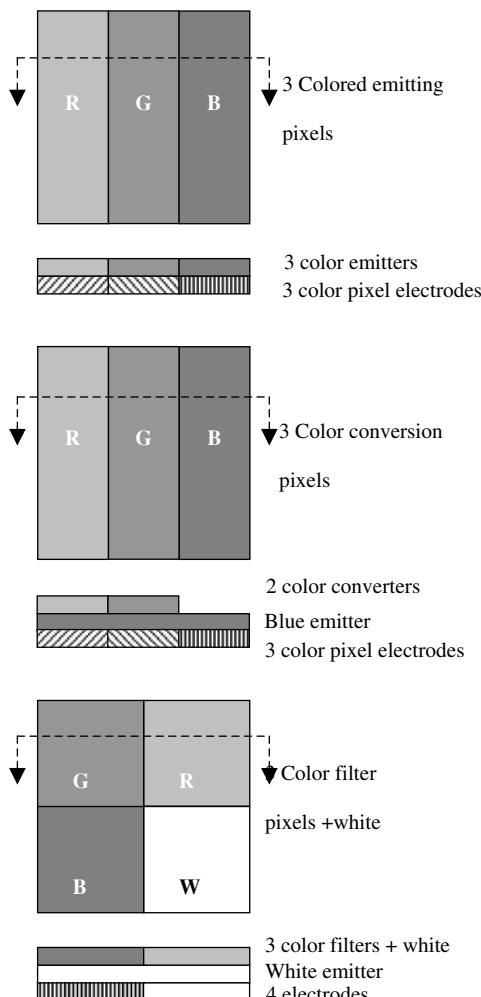

| 9.5.1     | Patterned RGB Color Filter                      | 286        |

| 9.5.2     | Patterned RGBW Color Filter                     | 286        |

| 9.5.3     | Patterned Red and Green Color Converters        | 288        |

| 9.5.4     | Patterned RGB OLED Layers                       | 288        |

| 9.5.5     | Stacked RGB Emitting Layers                     | 288        |

| 9.5.6     | Color Summary                                   | 288        |

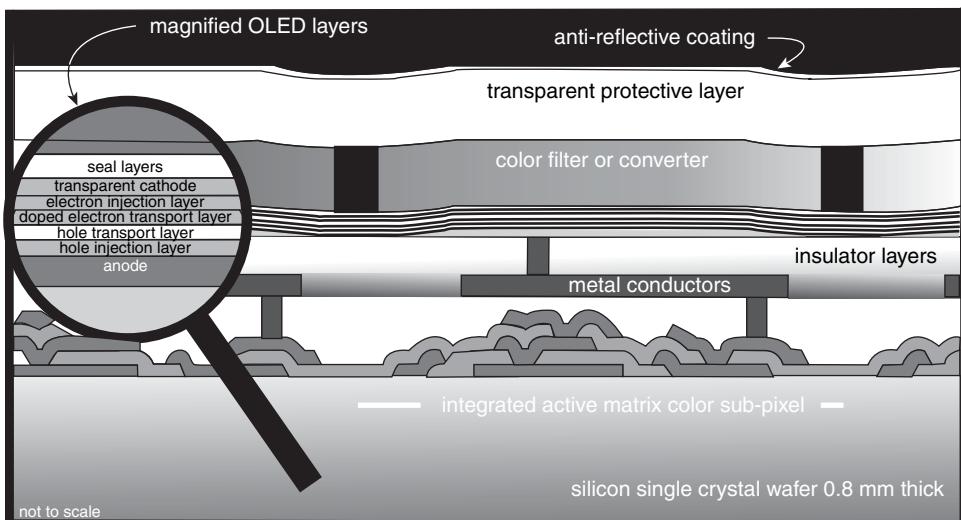

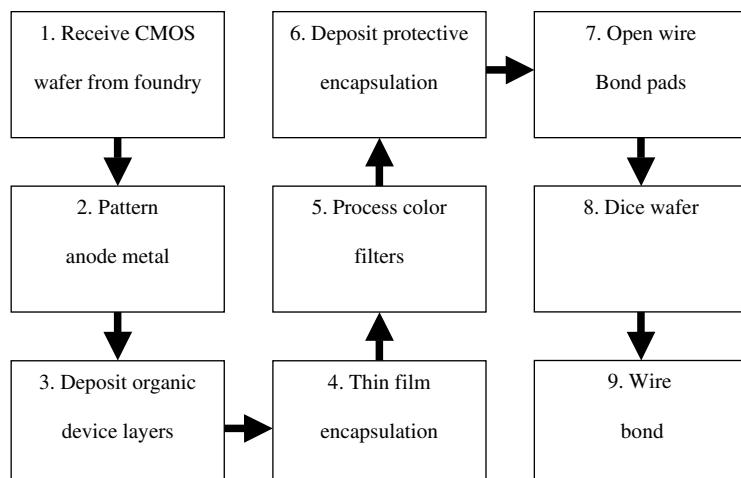

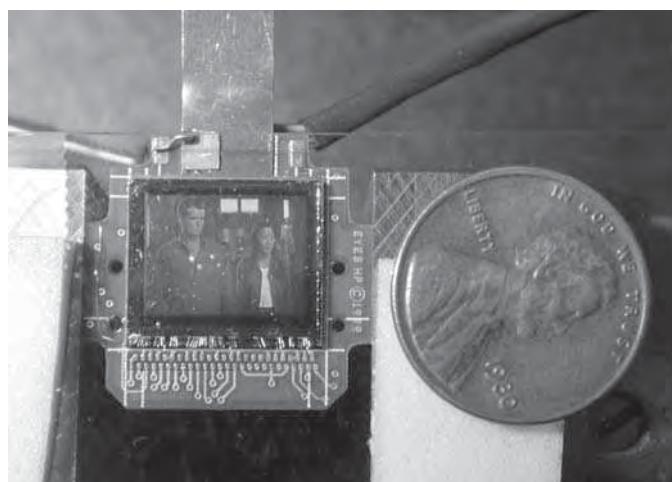

| 9.6       | OLED Microdisplays                              | 290        |

| 9.6.1     | General Properties of OLED Microdisplays        | 290        |

| 9.6.2     | Small-Molecule OLED (SMOLED) on Silicon Devices | 291        |

| 9.6.3     | Polymer OLED Microdisplays                      | 294        |

|            |                                            |            |

|------------|--------------------------------------------|------------|

| 9.7        | Other Emissive Microdisplays               | 297        |

| 9.7.1      | Inorganic Electroluminescent Microdisplays | 297        |

| 9.7.2      | Gallium Nitride Microemitter Arrays        | 298        |

| 9.7.3      | Porous Silicon Microdisplays               | 298        |

| 9.8        | Summary                                    | 301        |

| 9.9        | Bibliography                               | 302        |

| 9.10       | References                                 | 302        |

| <b>10.</b> | <b>Projection Displays</b>                 | <b>307</b> |

| 10.1       | Background                                 | 307        |

| 10.2       | Throughput                                 | 307        |

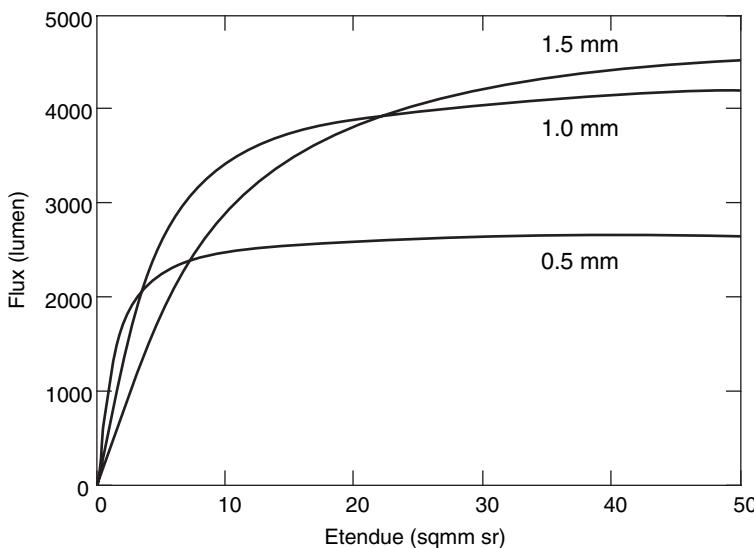

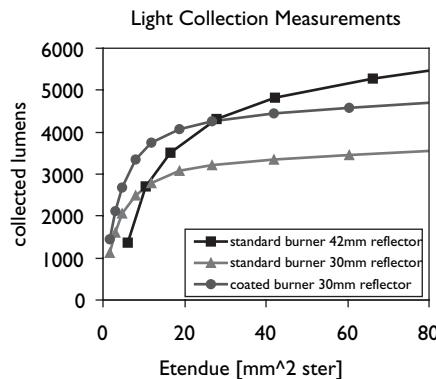

| 10.2.1     | Lumen Scale                                | 307        |

| 10.2.2     | Etendue Limit                              | 308        |

| 10.3       | Laser and LED Sources                      | 309        |

| 10.3.1     | Lasers                                     | 309        |

| 10.3.2     | Light Emitting Diodes                      | 310        |

| 10.4       | Arc Lamps                                  | 311        |

| 10.4.1     | Lamp Structure                             | 311        |

| 10.4.2     | Lamp Output                                | 312        |

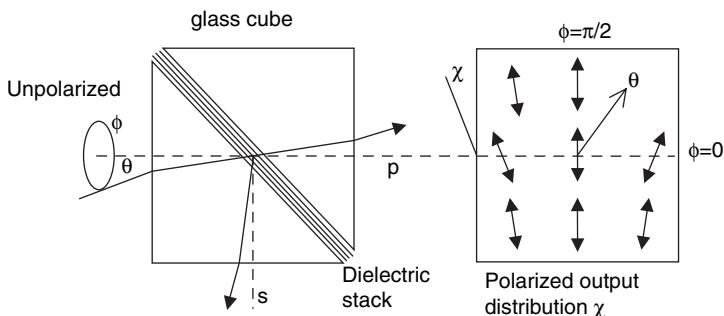

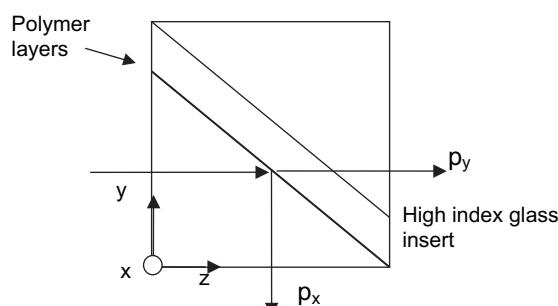

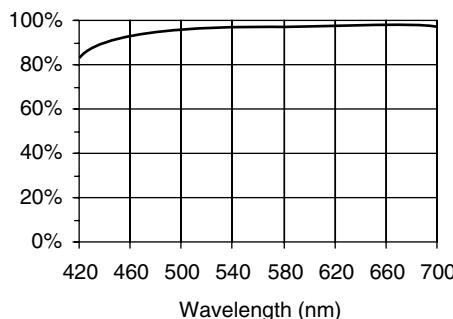

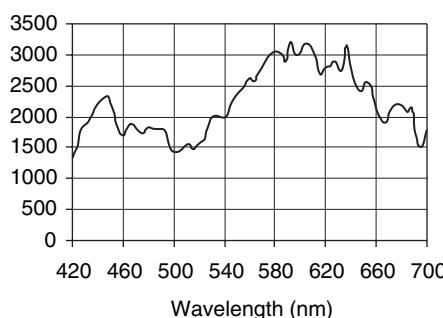

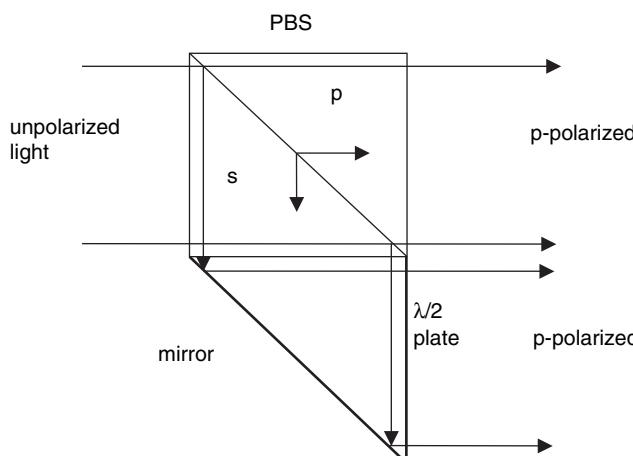

| 10.5       | Polarizing Optics                          | 313        |

| 10.5.1     | Absorbing Polarizer                        | 314        |

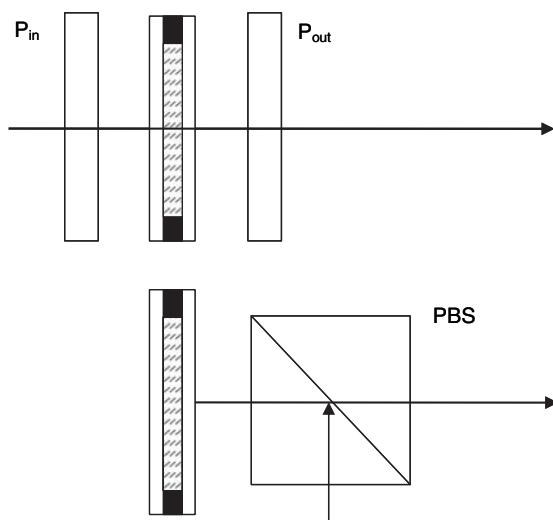

| 10.5.2     | Polarizing Beam-splitter                   | 314        |

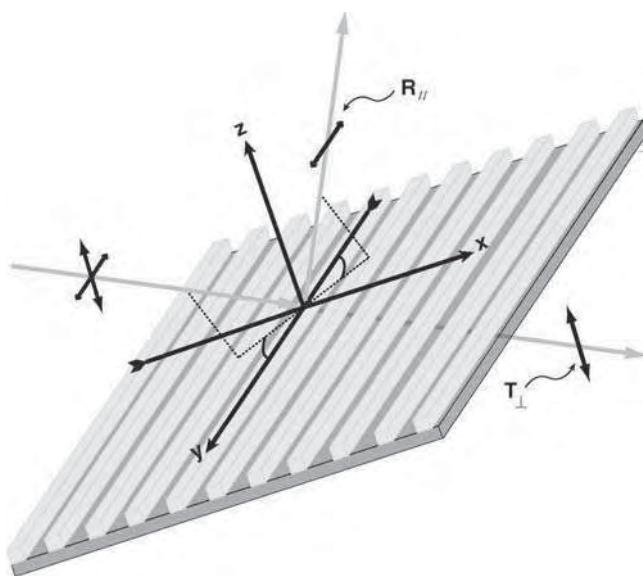

| 10.5.3     | Wire Grid Polarizers                       | 317        |

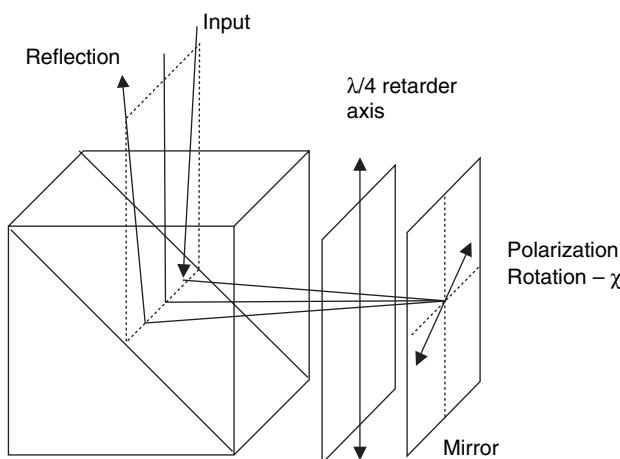

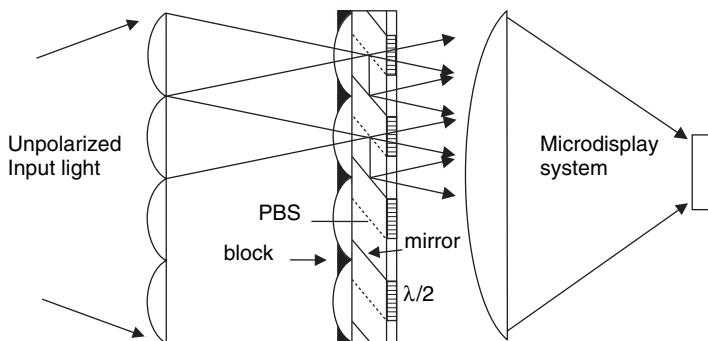

| 10.5.4     | Polarization Conversion                    | 319        |

| 10.5.5     | Optical Compensation                       | 321        |

| 10.6       | Color Management                           | 321        |

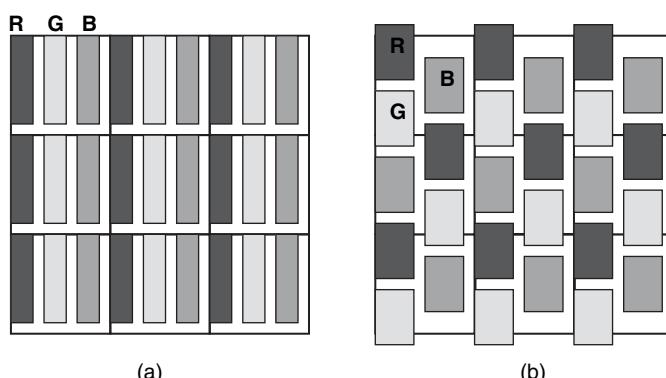

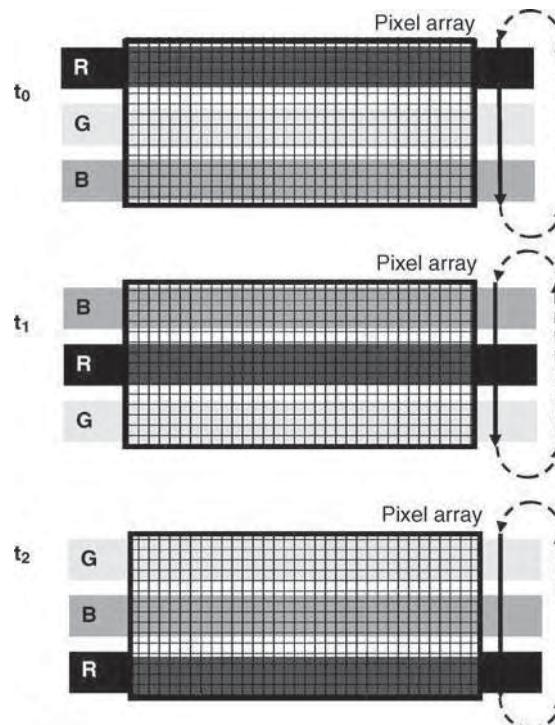

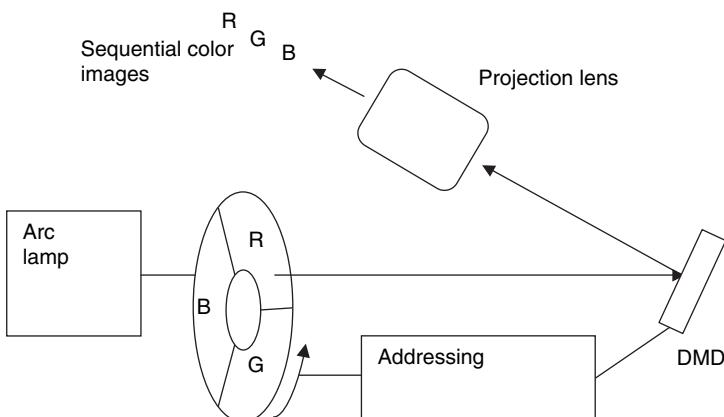

| 10.6.1     | Field-Sequential-Color                     | 322        |

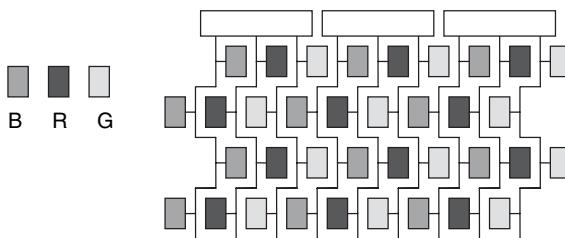

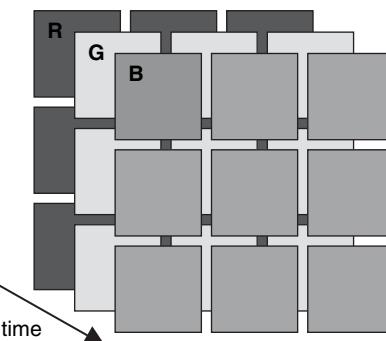

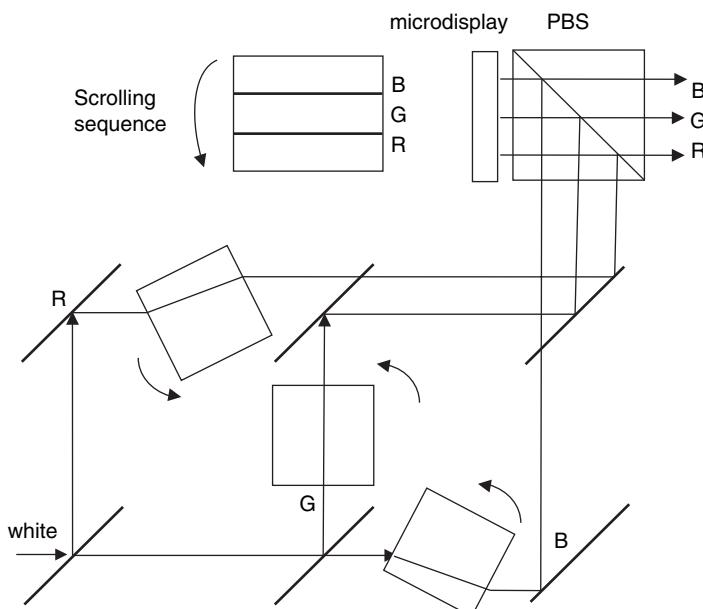

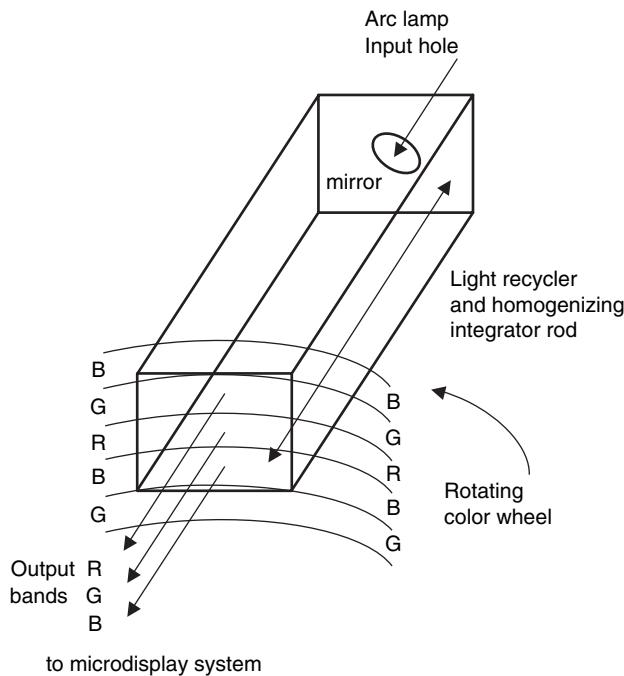

| 10.6.2     | Color Scrolling Systems                    | 323        |

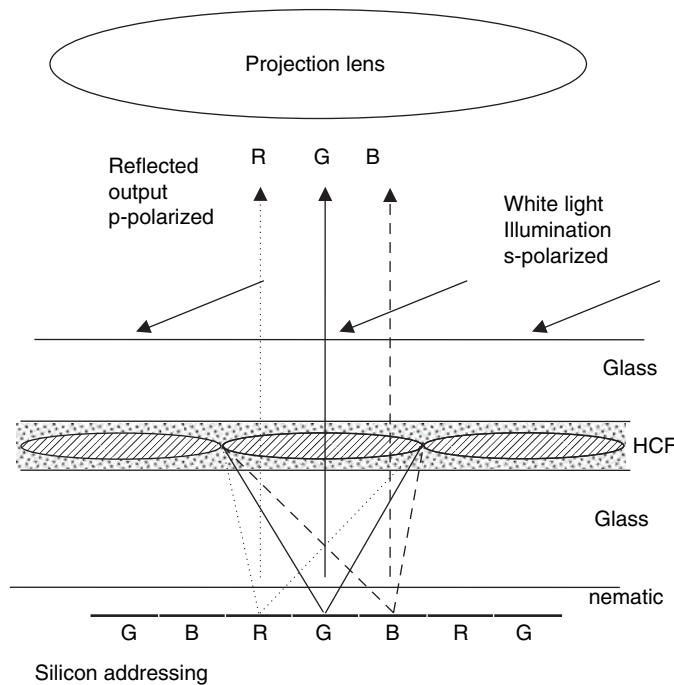

| 10.6.3     | RGB Pixel Systems                          | 325        |

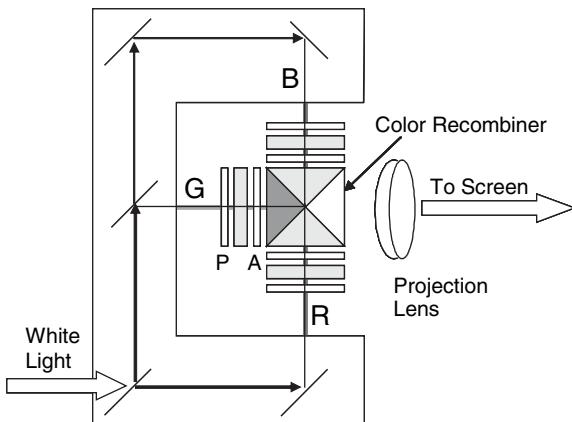

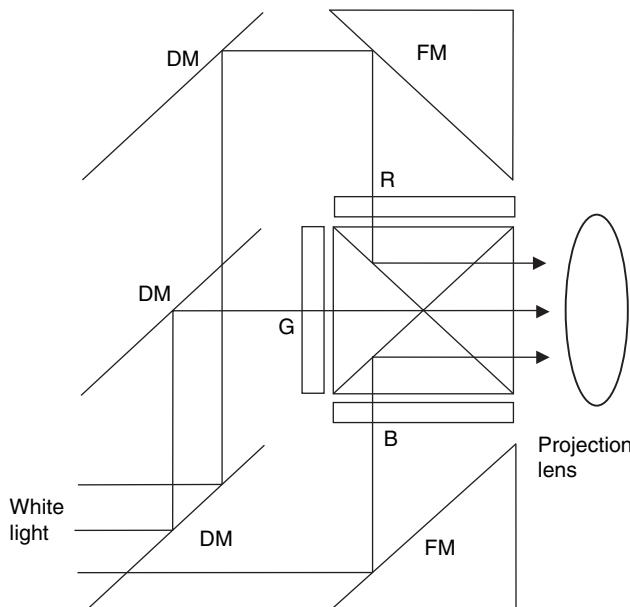

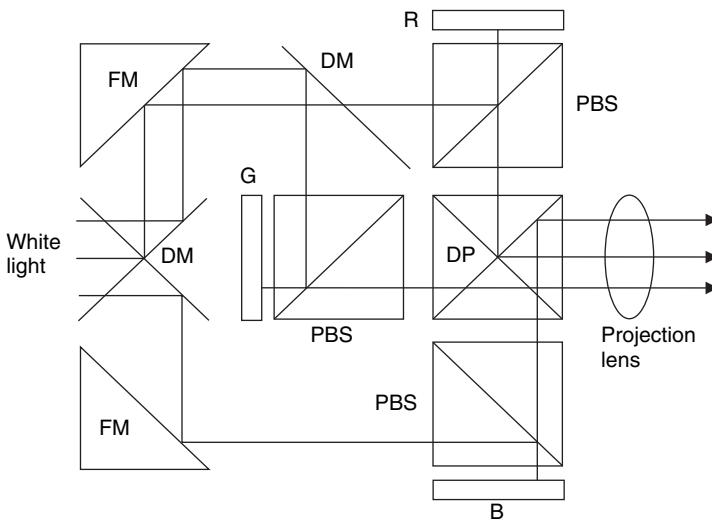

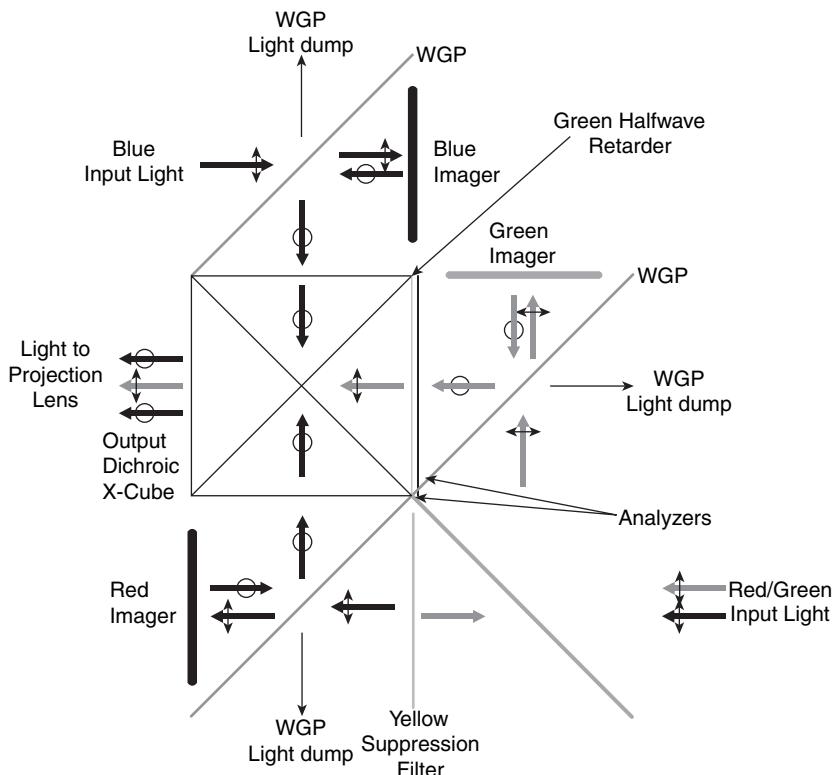

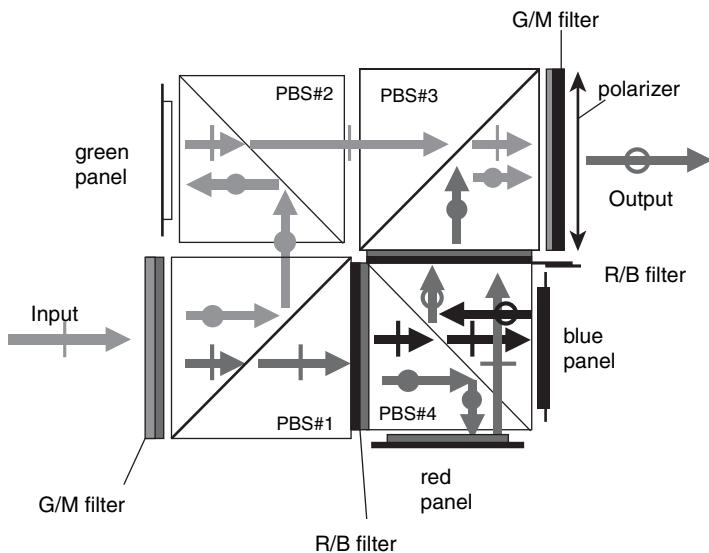

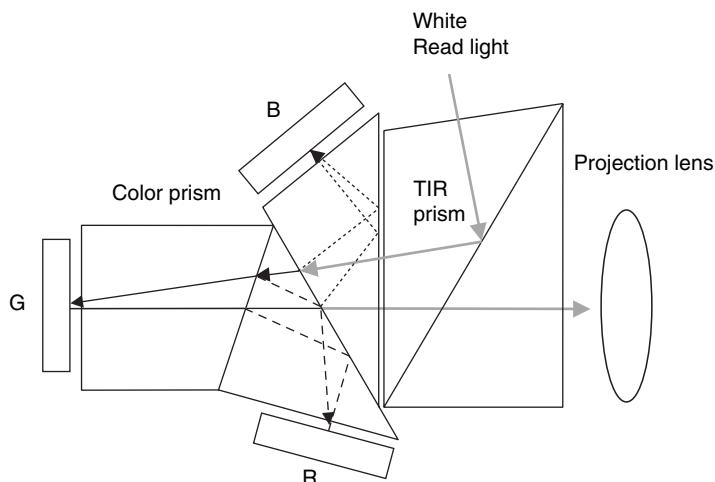

| 10.6.4     | Parallel Color                             | 326        |

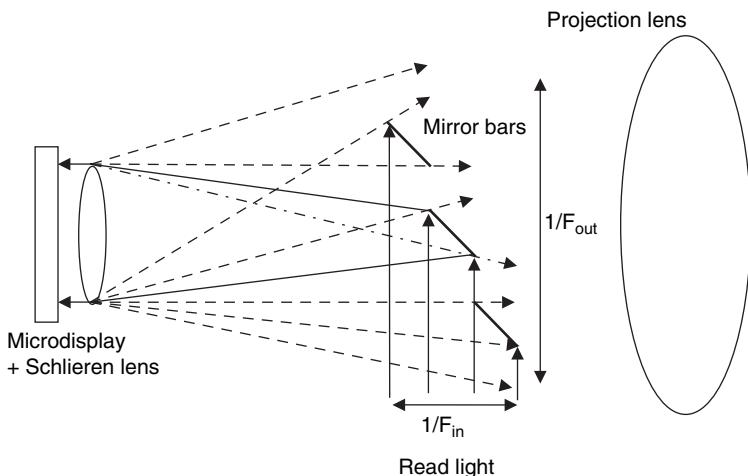

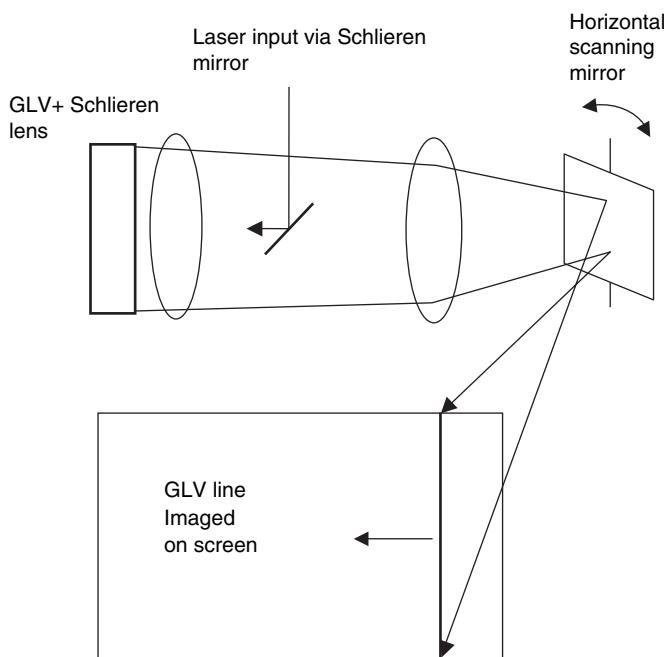

| 10.7       | Schlieren Projector                        | 330        |

| 10.8       | Laser Scanning                             | 330        |

| 10.9       | Projector Performance                      | 331        |

| 10.9.1     | Flicker                                    | 331        |

| 10.9.2     | Grayscale                                  | 332        |

| 10.9.3     | Lumen Output                               | 332        |

| 10.9.4     | Contrast Ratio                             | 332        |

| 10.9.5     | Color Uniformity                           | 334        |

| 10.9.6     | Resolution                                 | 334        |

| 10.10      | References                                 | 334        |

| <b>11.</b> | <b>Near-to-Eye Systems</b>                 | <b>337</b> |

| 11.1       | Background                                 | 337        |

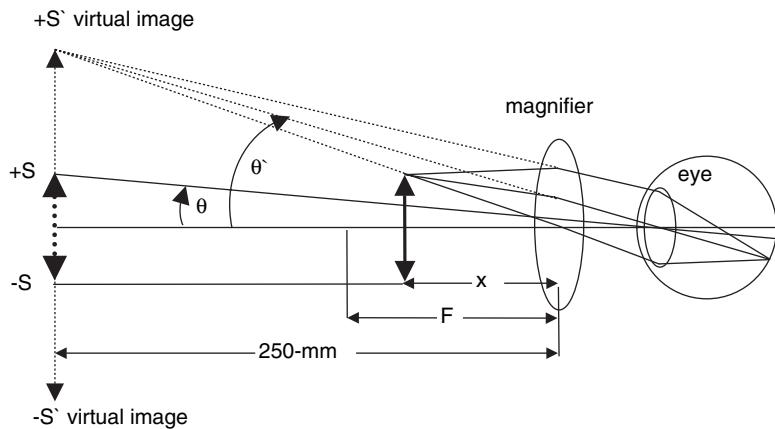

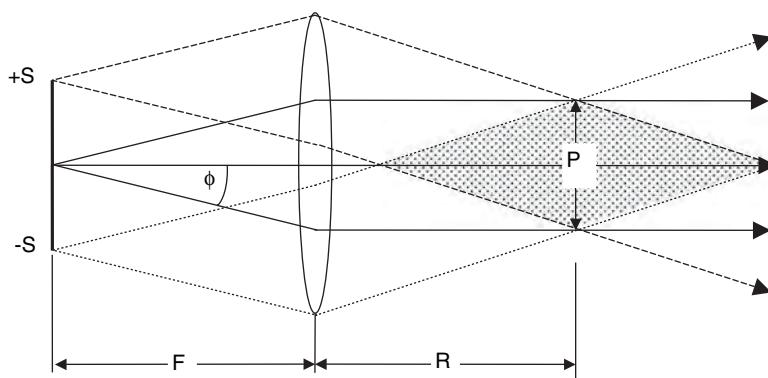

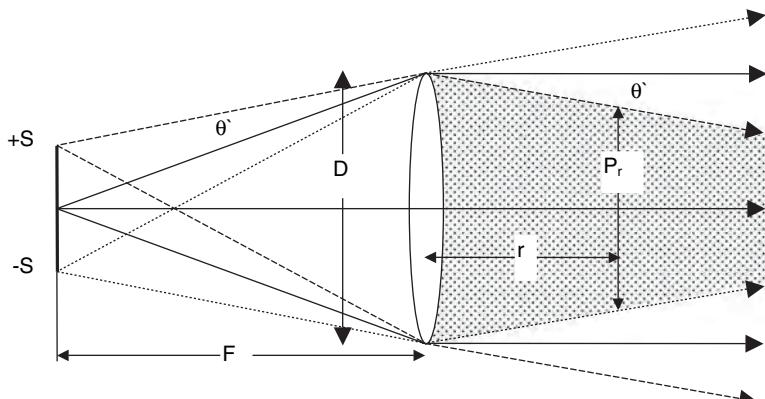

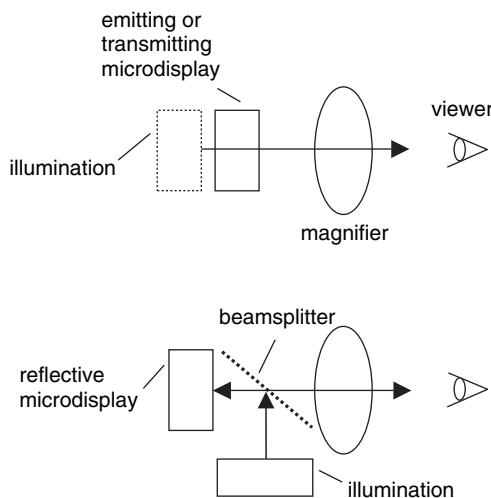

| 11.2       | Magnification                              | 337        |

| 11.2.1     | Virtual Image                              | 337        |

| 11.2.2     | Eyebox                                     | 338        |

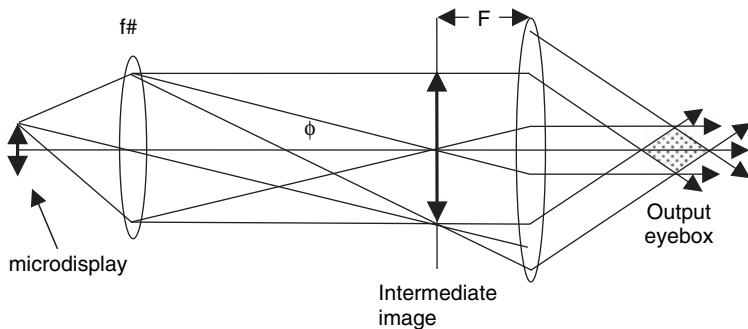

| 11.2.3     | Compound Magnification                     | 340        |

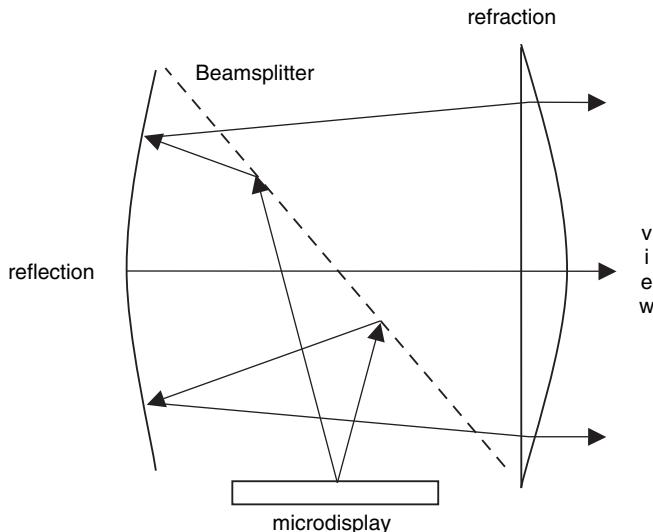

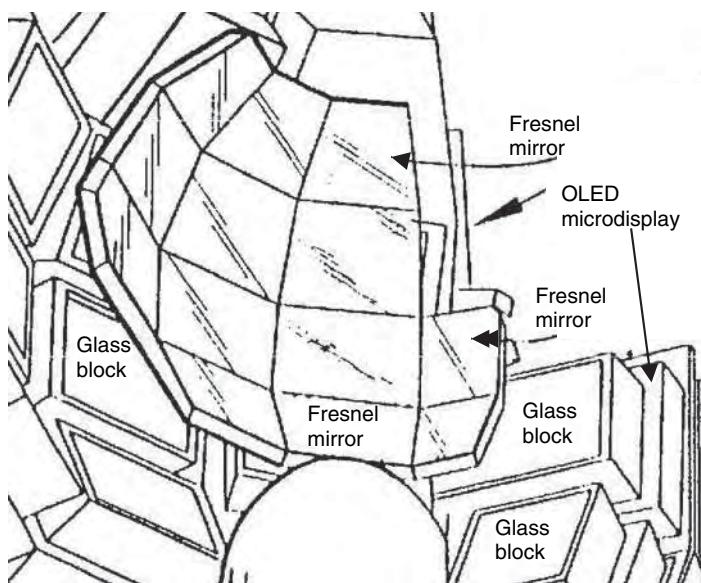

| 11.2.4     | Catadioptric System                        | 340        |

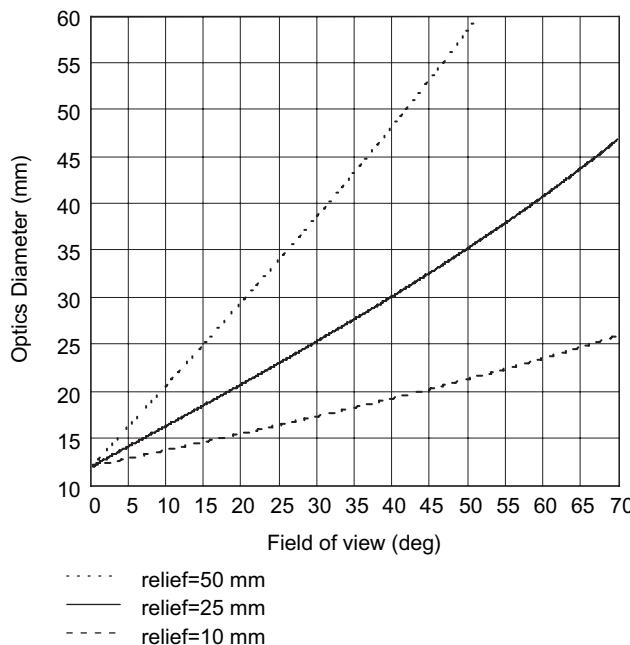

| 11.3       | Field of View                              | 341        |

| 11.4       | Microdisplay Factors                       | 342        |

|         |                         |            |

|---------|-------------------------|------------|

| 11.5    | Magnifiers              | 344        |

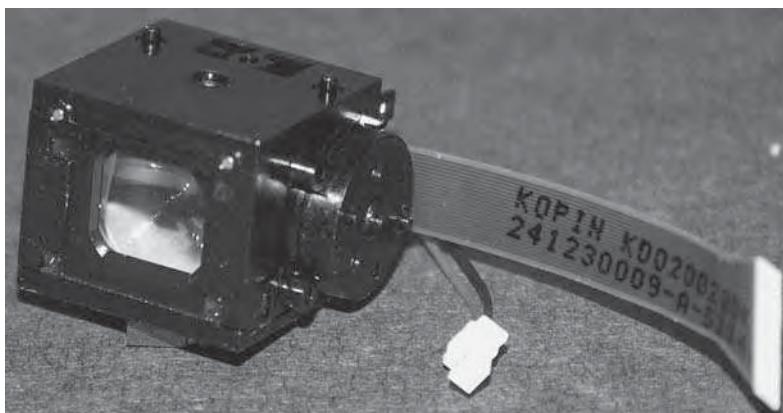

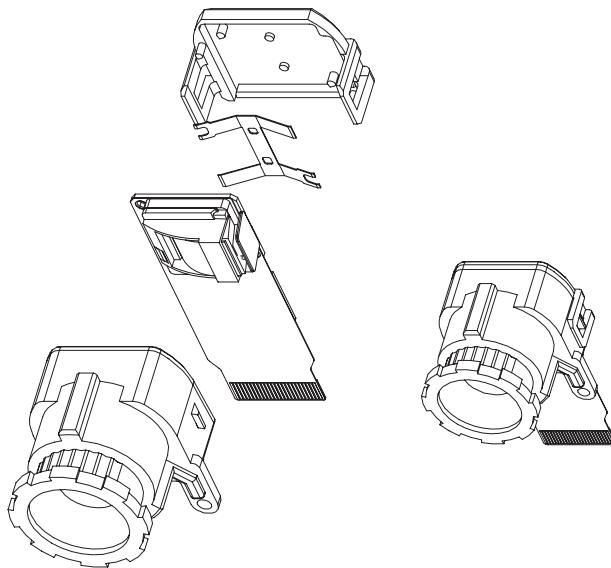

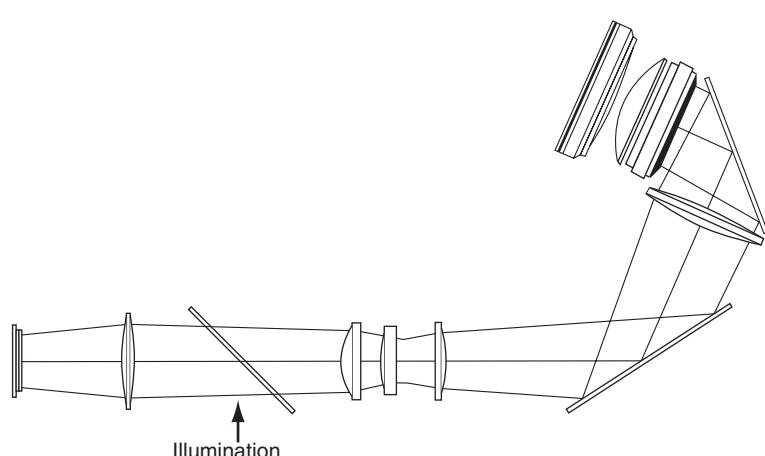

| 11.6    | Camera Viewfinder       | 345        |

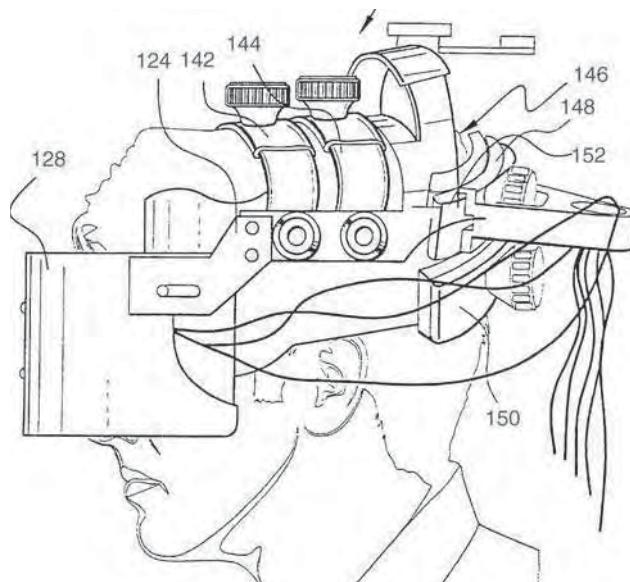

| 11.7    | Head-Mounted Displays   | 346        |

| 11.7.1  | General Considerations  | 346        |

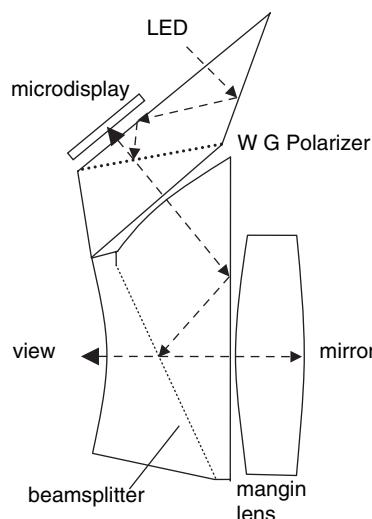

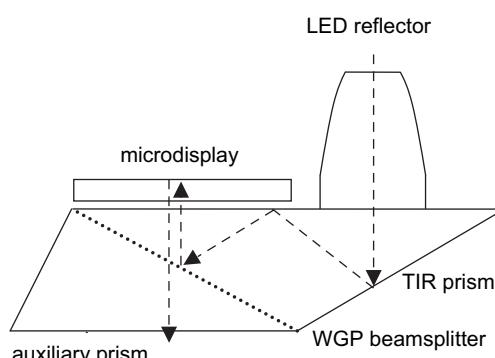

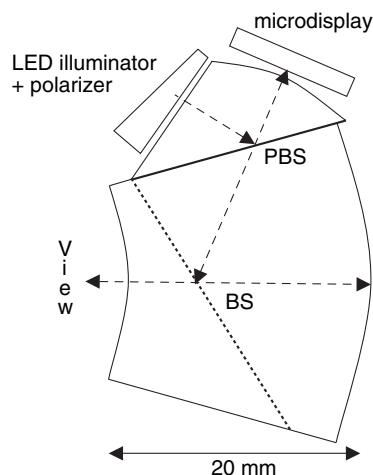

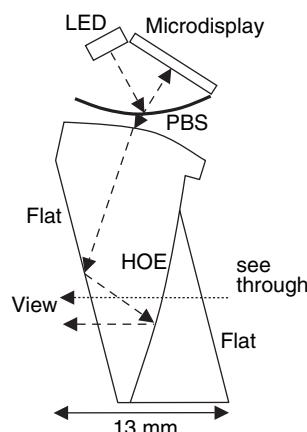

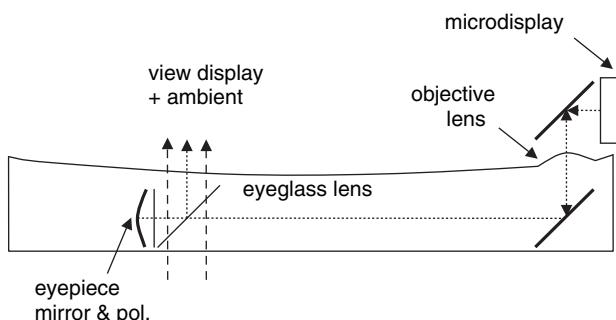

| 11.7.2  | TIR Prism               | 348        |

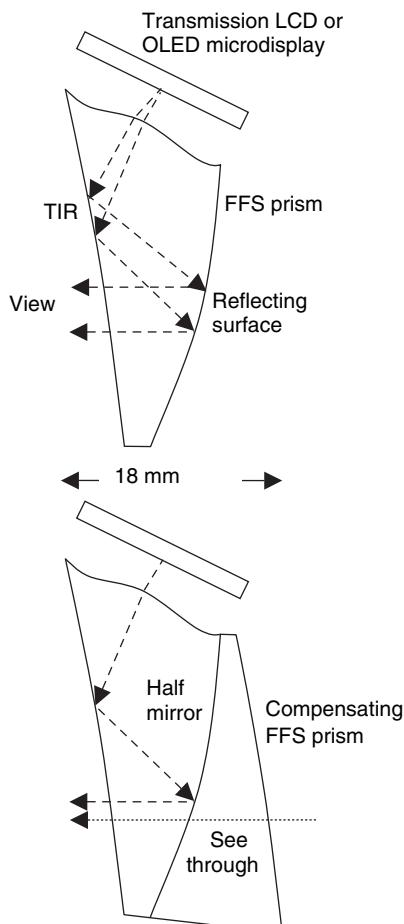

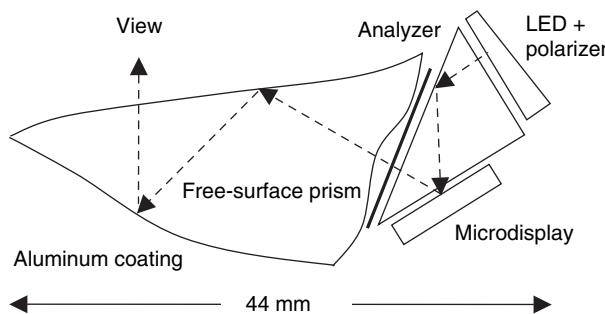

| 11.8    | Free-Surface Prisms     | 350        |

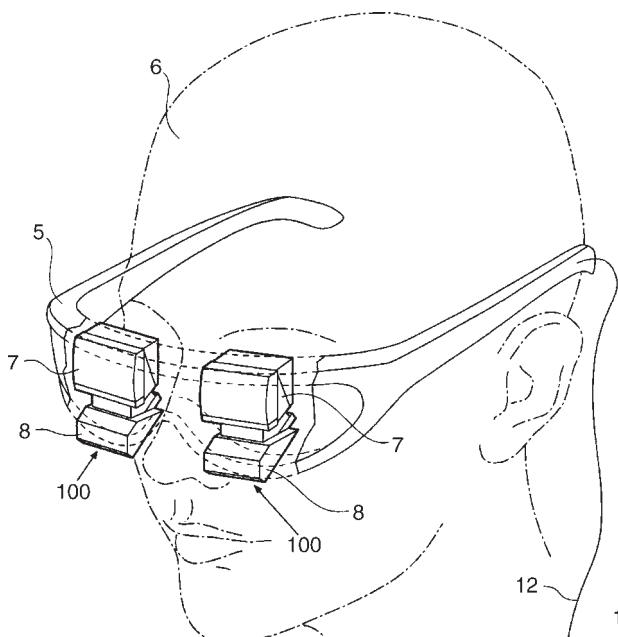

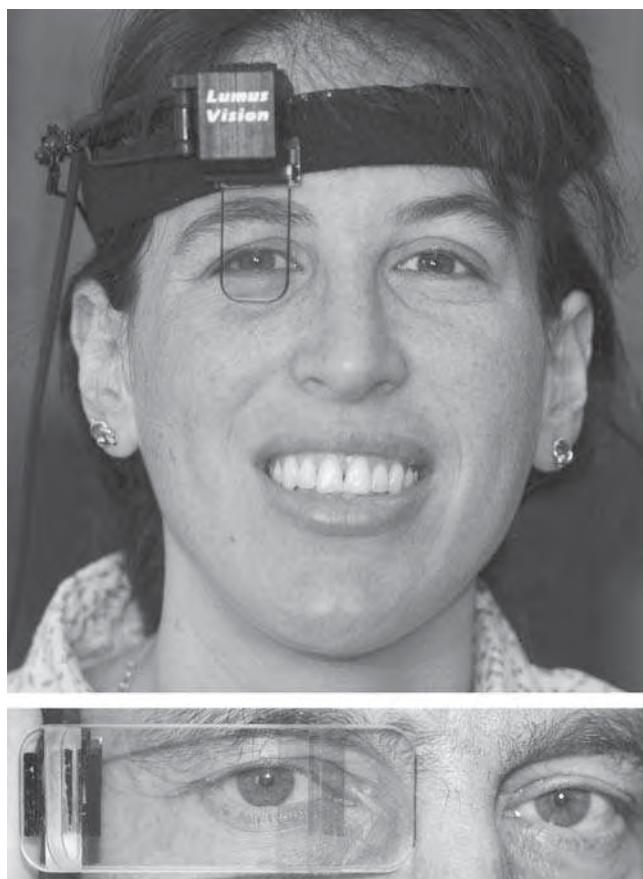

| 11.9    | Eyewear-based Displays  | 353        |

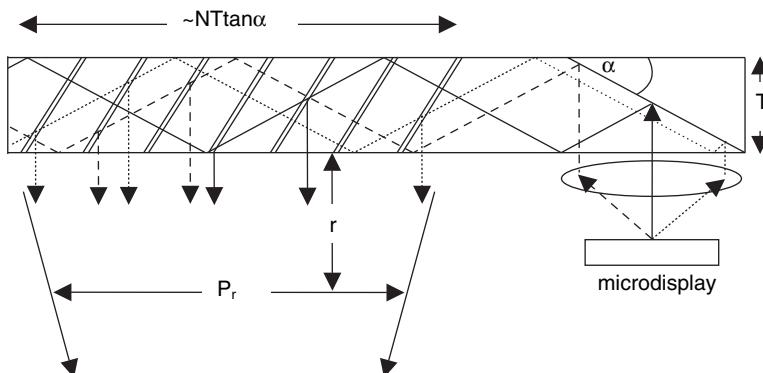

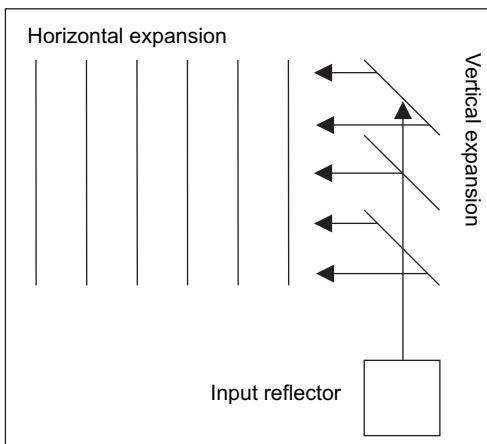

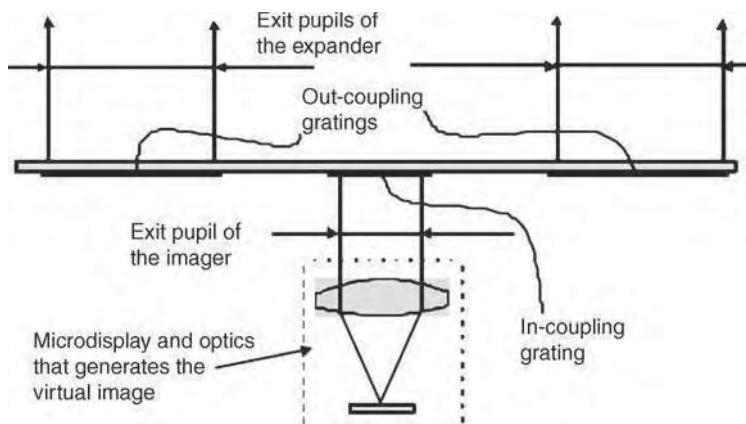

| 11.10   | Light-Guide Systems     | 354        |

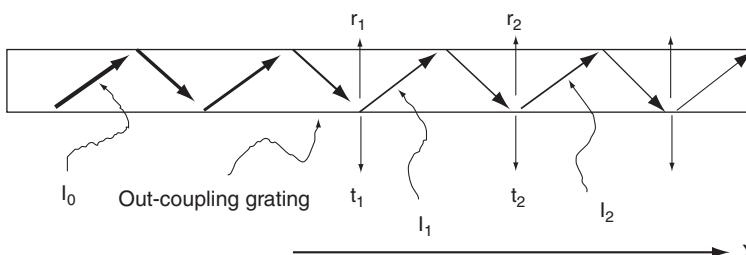

| 11.10.1 | Reflective Array        | 355        |

| 11.10.2 | Diffractive Array       | 357        |

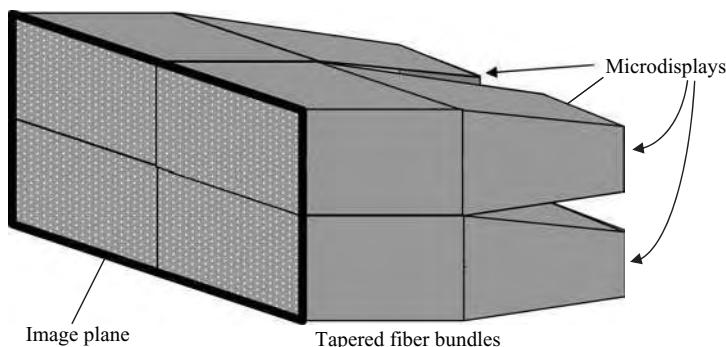

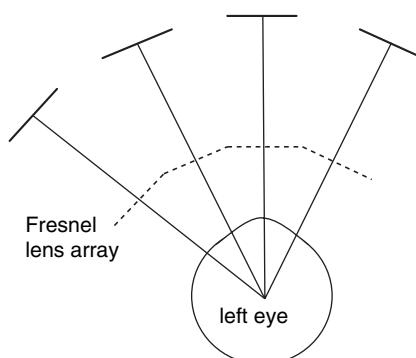

| 11.11   | Wide Field of View      | 358        |

| 11.11.1 | Single Microdisplay     | 358        |

| 11.11.2 | Tiled Microdisplays     | 359        |

| 11.12   | Portable Equipment      | 361        |

| 11.13   | References              | 362        |

|         | <b>Table of Symbols</b> | <b>365</b> |

|         | <b>Index</b>            | <b>371</b> |

# Series Editor's Foreword

---

There is an old saying that good things are worth waiting for and that is certainly true of this latest addition to the Wiley-SID Series. I only wonder at its title; the authors have been modest; this is much more than an Introduction. It is an in-depth treatment of the subject written by three experts in the field with extensive academic backgrounds, but with very differing experience outside academia. David Armitage has been a consultant to the industry for more than 20 years, Ian Underwood has founded and successfully floated his company on the London Stock Exchange and Shin-Tson Wu, after many years in industry, has returned to academia. Between them the authors bring a range of different and complementary knowledge and backgrounds to this work.

In the late 1970s, when David Armitage and I were working in IBM Research Division on liquid crystal effects for what would become known as LCOS displays, I do not believe that either of us anticipated the impact microdisplay technology would have or the economic importance it would achieve in the display industry. It is the basis of digital cinema, projection TV, computer projectors, near-to eye displays and some aspects of digital signage. The projection technologies that have become commercially successful on a large scale have been transmissive or reflective liquid crystal and micromechanical devices; the first based on polysilicon or transferred crystalline silicon and the other two on CMOS technology. Slower growth has occurred in head mounted and virtual reality displays. However, emissive OLED microdisplay technology is now appearing on the market and will surely drive increased growth of near-to-eye displays. It is a given that a dynamic and growing market will encourage the development of improvements to the existing technologies and the invention of new ones.

The book covers this commercially important and technologically diverse subject to a depth which will benefit engineers at many levels from practitioners in the field to potential users of microdisplays. The introduction provides a useful review of human factors, specifications, display technologies and applications. The second chapter covers all aspects of analog and digital addressing schemes for LCDs, DMDs and OLEDs and the next two discuss reflective and transmissive backplane technologies. There follow three chapters which deal respectively with transmissive LC microdisplays, reflective LC microdisplays and LCD assembly and testing. The next two chapters discuss the two important microdisplay technologies other than LCD; micromechanical and emissive (predominantly OLED) devices. The book concludes with two chapters on optical and psychophysical aspects of projection and near-to-eye systems.

Coverage of the subject is comprehensive not just in the sense that all the technical issues are addressed but because significant practical information relating to the economics of manufacturing and

assurance of product reliability are also included. General bibliographies are provided where appropriate and each chapter contains comprehensive references.

This twelfth book in the series is the first to deal exclusively with microdisplays and creates a welcome extension of our coverage into this important area.

**Anthony Lowe**

*Series Editor

Braishfield, UK*

# Preface

---

Devices that are now recognized as “microdisplays” have been around for many years, although the name itself is more recent. Initially, helmet-mounted miniature CRTs with magnifying optics delivered an image to an individual viewer, such as an aircraft pilot confined to a small cockpit. Personal display development demanded smaller, lighter-weight, lower-voltage alternatives to the CRT. In recent years, display designers have been presented with a range of microdisplay options satisfying many of their demands.

The flat panel dominance of direct view displays continues at small scale with advances in microdisplay projectors. Conference rooms quickly adopted the new lightweight projectors, replacing 35 mm slide shows and overhead transparencies with electronic images. Home TV projection followed, and today cinema projection is converting to microdisplays. Cinema is the most demanding application and shows electronic projection at its best, but at considerable expense. Film is long gone from home projection, which provides a huge potential market to support development and manufacturing of microdisplay projectors. The blossoming of high-definition television (HDTV), requiring higher resolution and larger screens, enhances the quest for market share amongst competing TV systems. Microdisplays are basic components of projection, having great influence on performance and price.

Display technology brings together a number of disciplines – chemistry, physics, materials science, electronics, mechanical engineering, optics, and others – in addition to which it involves other specialized areas such as visual perception and psychology. In 2002, Shin-Tson Wu, recognizing the need for a book bringing together various aspects of microdisplay design, fabrication, and application, invited David Armitage to co-author the work. The series editor, Tony Lowe, suggested that a third author, Ian Underwood, be added. The team would thus bring together a range of knowledge and experience that allows them to explain performance and clarify issues in microdisplay technologies and applications. In total, the authors of this book have injected more than 60 person-years of experience in microdisplay technology and applications into writing it. Responsibility for the structure and content of each individual chapter has resided with the author having the most relevant experience in the given topic area. General coordination of material and structure fell to David Armitage. As a guideline, we have erred a little on the side of repetition from chapter to chapter in order to allow each chapter to be read without too much cross-referencing to other chapters.

As part of the SID series, the book serves the display community, but also accommodates readers unfamiliar with display details. Many engaged in the display industry concentrate on a particular discipline such as electronics or optics; others are limited to segments such as direct-view LCD, or plasma display. The book offers easy access to microdisplay details for readers seeking to broaden their background.

We examine the dominant microdisplay forms in detail, revealing their strengths and weaknesses. Microdisplays that once attracted attention are discussed briefly, noting the reasons for their decline. Others that are in the early stages of development are mentioned in relation to their promise. A range of basic projection system designs are discussed in relation to different microdisplay types. Other important projection components, such as light sources and polarizing beam-splitters, relate to microdisplay aspects. The need to provide compactness and viewing comfort as well as magnification complicates the optics of personal displays. A review of several successful designs includes output-pupil expansion techniques to enhance viewing comfort.

The introduction places microdisplays in context and discusses human factors such as visual acuity and flicker that influence the design of all display systems. The second chapter is concerned with electronic addressing methods, particularly the digital techniques supported by silicon backplane devices. A chapter devoted to silicon technology charts development of the silicon backplane structure with evolution of the silicon fabrication industry in general. The chapter on transmission microdisplays highlights the challenge of maintaining a high aperture ratio under pressure of shrinking pixel size. Two chapters on liquid crystals cover the design options and address the field fringing issues of concern in microdisplays. The chapter devoted to the burgeoning field of electromechanical systems emphasizes the development of the DMD microdisplay. An emissive microdisplays chapter is dominated by OLED development to complete the coverage of microdisplay devices. The final chapters are devoted to applications areas – projection then near-to-eye.

The authors thank Tony Lowe (Editor) and Mike Jin (SpatiaLight) for their initial comments on the content and structure of the book. We thank members of the display community for supplying pictures and diagrams that enliven and clarify the text. We are particularly indebted to: Larry Hornbeck (Texas Instruments); Bob Melcher (Syntax-Brillian Corporation); Professor Ifor Samuel (St Andrews University); Professor Bill Crossland (Cambridge University); Dr Euan Smith and Terry Nicklin (Cambridge Display Technology Ltd) for supply of, and permission to reproduce, information and diagrams relating to polymer OLED materials and devices; MicroEmissive Displays Ltd for supply of, and permission to reproduce, information and diagrams relating to polymer OLED microdisplays; the University of Edinburgh for supply of, and permission to reproduce, information and diagrams relating to LCOS backplanes. Ian Underwood offers his grateful thanks to colleagues including Dr Georg Bodammer, Dr Alastair Buckley, Dr Dwayne Burns, Dr Christophe Miremont and Graeme Kelly for their helpful feedback on his drafts. Shin-Tson Wu is indebted to his post doctors and students for technical assistance, especially Dr. Xinyu Zhu and Dr. Simon Fan-Chiang for providing the simulation results.

### ***About the Authors***

David Armitage pursued academic interests in semiconductor and liquid crystal physics, leading to microdisplay activity at IBM and Lockheed Corporation. For many years, he has consulted in microdisplay development and applications. He has numerous publications on semiconductors, liquid crystals, and displays. Academic qualifications include PhD (Physics), Bath University, UK; MS (Physics), University of Newcastle-upon-Tyne, UK; BS (EE), Durham University, UK.

Ian Underwood entered the field of LCOS as a postgraduate student in 1983. For the next 16 years he was part of a research group that pioneered advances in LCOS devices and applications. In 1999 he shifted his attention to P-OLED microdisplays when he co-founded MicroEmissive Displays which he continues to serve today as Director of Strategic Marketing. Personal distinctions include a Fulbright Fellowship held at the University of Colorado (1991), the Ben Sturgeon Award of the UK chapter of SID (2000), seminar presenter at the SID Annual Meeting (2000 to 2004), the Alfred Woodhead best paper award of the UK chapter of SID (2002 and 2004), Ernst & Young Emerging Entrepreneur of the Year (2003), Fellow of the Royal Society of Edinburgh (2004), the Gannochy Award for Innovation of the Royal Society of Edinburgh (2004), and a keynote address on Microdisplays at Eurodisplay IDRC in 2005. In 2004 he was named Professor of Electronic Displays at the University of Edinburgh.

Shin-Tson Wu is a PREP professor at the College of Optics and Photonics, University of Central Florida (UCF). Prior to joining UCF in 2001, Dr Wu worked at Hughes Research Laboratories (Malibu, California) for 18 years. He received his PhD from the University of Southern California and his BS in physics from National Taiwan University. His studies at UCF concentrate on liquid crystal displays, liquid crystal materials, foveated imaging, tunable-focus liquid crystal/liquid lenses, bio-photonics, and laser beam steering. Dr Wu is a Fellow of the IEEE, SID, and OSA. He has co-authored **three** books: *Fundamentals of Liquid Crystal Devices* (Wiley-SID, 2006), *Reflective Liquid Crystal Displays* (Wiley-SID, 2001), and *Optics and Nonlinear Optics of Liquid Crystals* (World Scientific, 1993), **five** book chapters, and over 300 papers.

# 1

# Introduction

---

## 1.1 *Microdisplays*

Advances in several technologies related to projection displays and near-to-eye (NTE) displays have intensified interest in these areas. Development of the microdisplay is a key technology. The term “miniature display” does not distinguish small displays, such as watch displays, from displays designed with magnification in mind as indicated in Figure 1.1.<sup>1</sup> Microdisplays are a natural extension of the familiar microfilm, where magnification is essential to readout. A coarse image is recognizable on a microdisplay, but the full resolution is only discernable with the aid of magnification. The term “microdisplay” now in general use means a compact display designed for use with a magnification system. Microdisplay projectors have taken over the consumer market from CRT projection displays that have long dominated large-screen television. NTE products such as camera viewfinders and head-mounted displays evolve with microdisplay developments.

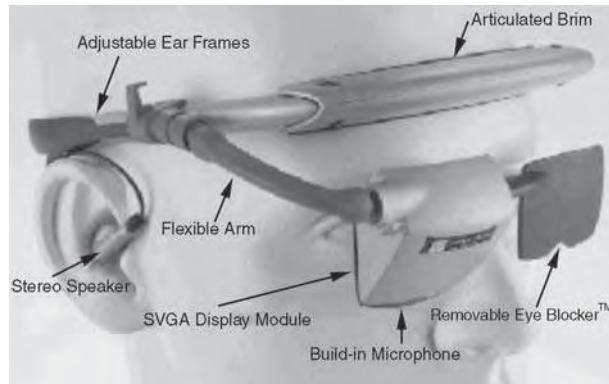

The direct-view CRT display has grown bigger and better over the years. Competing flat panel technologies such as liquid crystal and plasma displays have followed a similar path. Conversely, microdisplays have become smaller, in step with the shrinkage in microelectronics. NTE displays have progressed from miniature CRTs to lightweight microdisplays with superior characteristics. Attractive image quality and improvements in viewing comfort have opened up a commercial market for NTE displays. Figure 1.2 shows an early head-mounted display (HMD) designed for the consumer market, employing dual liquid crystal microdisplays. The unit weighs 150 gm and simulates a 52-inch diagonal color image viewed from a distance of 7 ft with resolution  $260 \times 346 \times 3$  RGB pixels.

The vacuum tube nature of the CRT has made it difficult to expand in scale over the years, and now appears to be saturating at a cumbersome 40-inch diagonal. Projection displays powered by special-purpose compact CRTs overcame the size limitation. In comparison, the simple slide projector provided a much better image, and obviously with the invention of a suitable “electronic slide” (microdisplay) would be the basis of a new video projection technology. A wide variety of electro-optic devices has struggled to fill the microdisplay role in projectors. The current choices,

## 2 INTRODUCTION

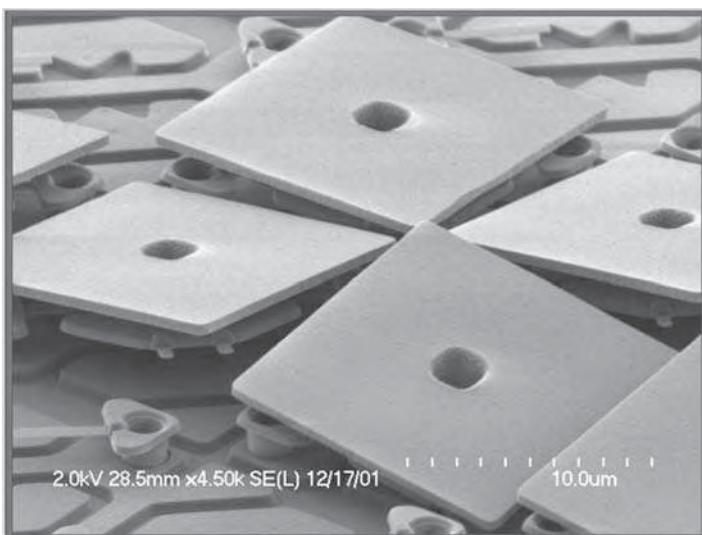

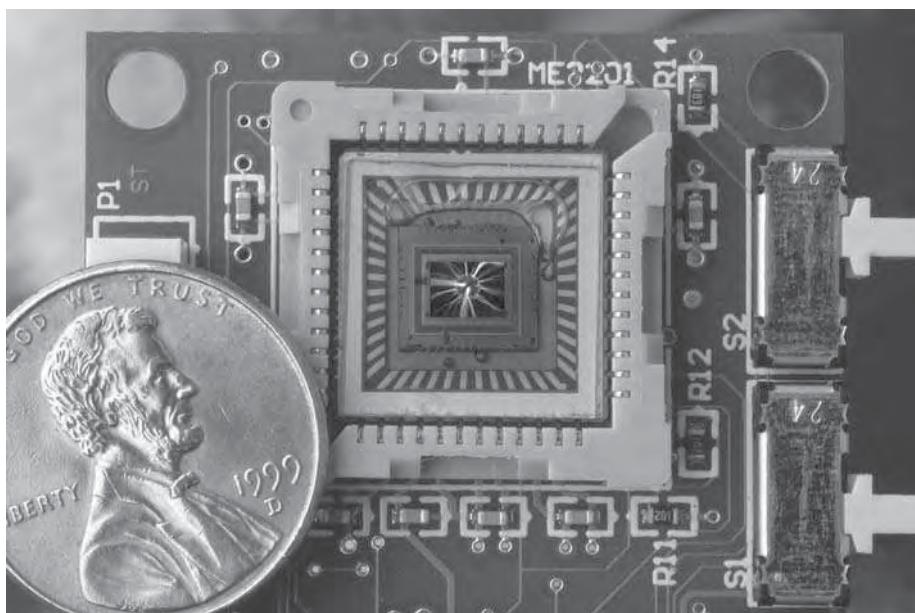

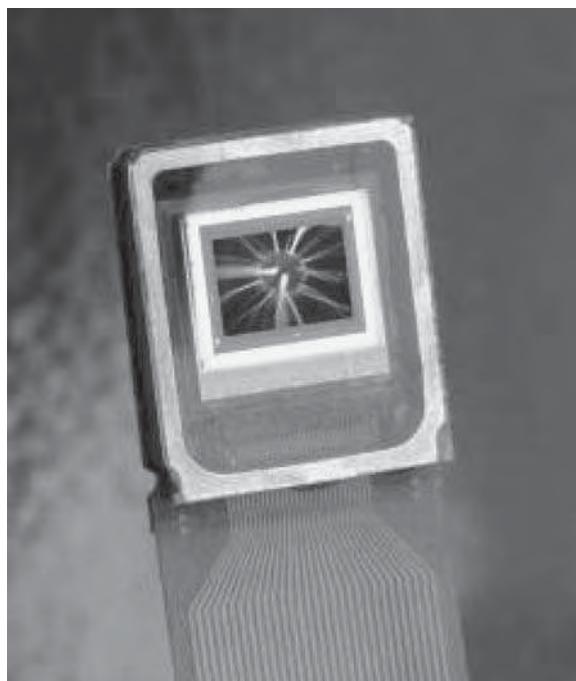

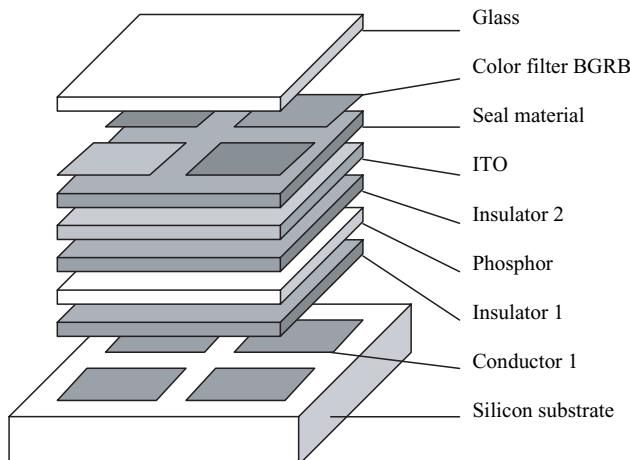

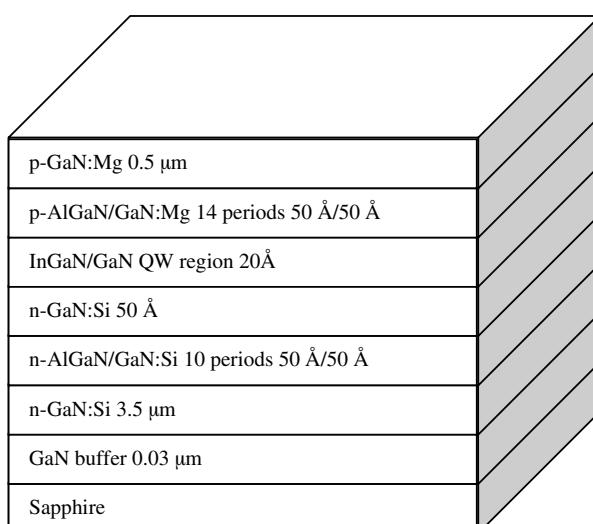

**Figure 1.1** Miniature watch display compared with microdisplay having  $9\text{ }\mu\text{m}$  pixel pitch,  $1920 \times 1080$  resolution giving active area 0.78-inch diameter. Reprinted courtesy of Sony Corporation

liquid crystal and micromechanical devices, have proved commercially viable and will be difficult to displace. Price continues to exert a downward pressure on microdisplay area, due to the device cost and the influence of area on system cost. Figure 1.3 shows a portable business projector weighing 2.4lb, with dimensions  $2.6 \times 6.1 \times 7.8$  inch, employing a single micromechanical microdisplay of  $1024 \times 768$  resolution, diagonal 0.7 inches (DMD<sup>TM</sup>), projecting full-color 1500 ANSI lumens at contrast ratio 1100:1.

Rear projection TV is a huge consumer market that drives the development of microdisplays. The latest products employ folded optic systems that reduce the unit depth to about 8 inches eroding the

**Figure 1.2** Head-mounted microdisplay GT270. Reprinted courtesy of Canon Inc.

**Figure 1.3** Microdisplay portable business projector LP70+. Reprinted courtesy of InFocus Corp.

space advantage of flat panel displays. The highest quality products produce the best images of any display technology. Figure 1.4 shows a 65-inch diagonal rear projection TV, employing three XGA LCOS microdisplays: luminance  $450\text{ cd/m}^2$ , contrast ratio 2000, weight 95 lb.

## 1.2 Human Factors

The display engineer needs some knowledge of human vision to understand display performance and comfort for a given application. An engineering specification of human vision provides details of resolution, sensitivity, response time, and wavelength dependence. Luminance measured in  $\text{candela/m}^2$  ( $\text{lumen/steradian/m}^2$ ) is a measure related to our sensation of brightness. The lumen is a photometric unit of light flux derived from the product of the eye's wavelength sensitivity and radiant power,

**Figure 1.4** Microdisplay rear-projection TV model BR768HC. Reprinted courtesy of Syntax-Brillian Corp.

## 4 INTRODUCTION

giving the visual response to different wavelengths directly. At peak wavelength sensitivity 555 nm, flux in lumens = 683 (radian flux in watts); the same radiant flux at any other wavelength is worth fewer lumens, falling to zero lumens outside the visible wavelength range. Ambient light, contrast, and color saturation also influence our sense of brightness.

### 1.2.1 Color

Perception of color depends on wavelength in a complicated way that allows three primary wavelengths to represent a wide color gamut according to the luminance values of the primaries. Red, green, and blue primaries (RGB) optimize the color gamut. An even wider gamut of colors follows from the addition of more primaries. The narrower the spectral range of each primary color, the more saturated the primary color becomes.

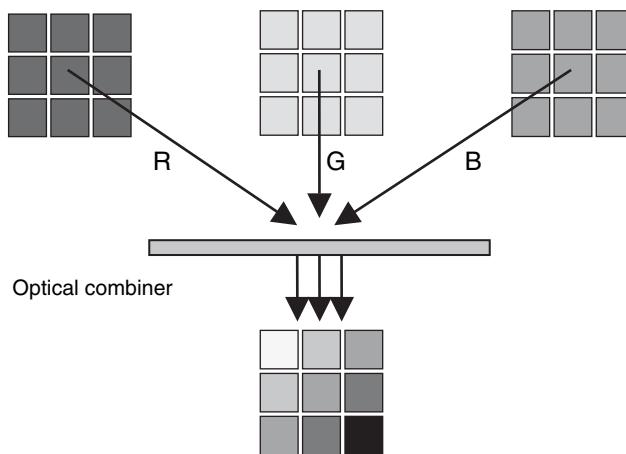

Reduction to three primaries is of great utility in electronic displays, where picture elements (pixels) grouped in RGB triads below visual resolution merge to provide a full-color display. Color pixels are standard for direct-view CRT, flat panel displays, and some microdisplays. One of the options in projector design is to superimpose primary color images on the screen, to achieve full color. Each primary has a dedicated microdisplay, requiring three microdisplays for this parallel color system. Alternatively, color sequential display systems exploit the eye's response time by presenting the primary colors in rapid succession to give the perception of a single color represented by the primaries. One microdisplay can handle the sequence of colors, but it must operate at high frame rate. Eye movement during the color sequence will cause some separation of primary colors on the retina, perceived as color breakup. Eye movement sets a lower limit on the color field rate needed to suppress color breakup.

Color temperature is a measure of the spectral distribution of a light source, by comparison with the temperature of equivalent black body radiation. A color temperature of 6504 K represents average daylight. An arc-lamp source can be adjusted to a given color temperature by spectral filtering, with some sacrifice in output. Primary color separation requires filtering, where strong color saturation incurs further loss. Some compromise between color temperature, color saturation, and luminance is required. Color vision is lost at low light level  $<10^{-4} \text{ cd/m}^2$ ; display engineering is essentially concerned with substantially higher luminance levels to provide good color vision.

### 1.2.2 Resolution

Display costs generally increase with resolution, making it wasteful to provide display resolution beyond viewer requirements. Light level, modulation depth, and wavelength of the signal influence eye resolution, peaking at maximum sensitivity 555 nm. The response to one-dimensional sinusoidal luminance patterns characterizes eye resolution as a function of spatial frequency ( $u$ ), luminance ( $L$ ), and contrast ( $C$ ).

$$\text{Contrast ratio } CR = \frac{L_{\max}}{L_{\min}} \quad (1.1)$$

$$\text{Contrast } C = \frac{L_{\max} - L_{\min}}{L_{\max} + L_{\min}} = \frac{CR - 1}{CR + 1} \rightarrow 1 - \frac{1}{CR} \quad (1.2)$$

$$\text{Perception boundary } L = L_{\text{av}} [1 + C_{\min} \sin u] \quad L_{\text{av}} = \frac{L_{\max} + L_{\min}}{2} \quad (1.3)$$

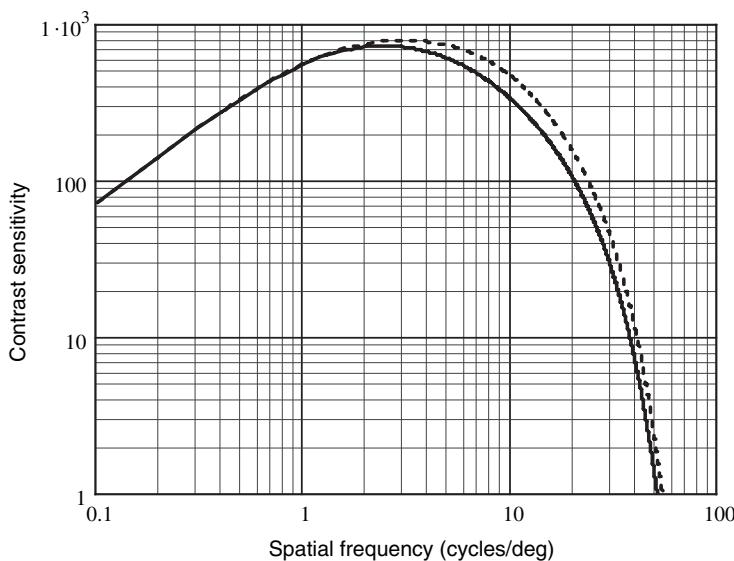

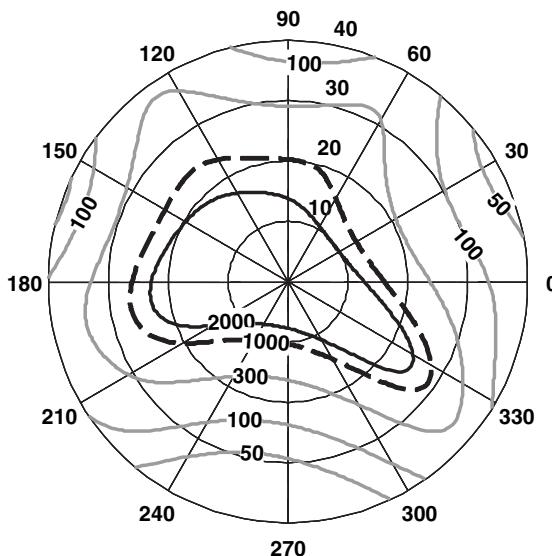

The contrast sensitivity function  $S(u, L_{\text{av}}) = 1/C_{\min}$ , where  $C_{\min}$  is the minimum contrast required to perceive the sinusoidal fringes at spatial frequency  $u$  and average luminance  $L_{\text{av}}$ . Contrast sensitivity plots reveal the most sensitive spatial frequency and upper frequency cutoff. Figure 1.5 shows contrast

**Figure 1.5** Contrast sensitivity for luminance: solid line  $100 \text{ cd/m}^2$ ; dotted line  $900 \text{ cd/m}^2$

sensitivity plots appropriate to displays. The plots are generated from formulae derived from a signal processing description of human vision, with parameters fitted to reported data.<sup>2</sup> Peak contrast sensitivity is about 4 cycles/deg, and cutoff about 60 cycles/deg, consistent with a limiting angular resolution of 0.5 minute of arc applicable to edge detection, and comparable with an accepted average value of 1 minute for human visual acuity. Increase in luminance provides a small increase in resolution at display luminance levels. The frequency cutoff corresponds to foveal vision, which is limited to about 2 degrees field of view. Eye and head movement compensate the limited field of view of the eye at high resolution, creating the impression of high resolution over a wide angle. Restriction of natural eye and head movement has a disturbing effect on vision that can result in eyestrain and discomfort.

The lower sensitivity of non-foveal vision contributes to the decline in sensitivity at low spatial frequency, where the spatial wavelength extends beyond the foveal range. Further low-frequency attenuation occurs at the neural processing level. Gradual variation in luminance of order 50% from the center to boundary of a display may not be noticeable, while shifts less than 1% are obvious at sensitive spatial frequencies. Color uniformity is similarly sensitive to spatial frequency. Moreover, we are more sensitive to color change than luminance change at low spatial frequency, making color uniformity more difficult to achieve in display systems.

Correlation in the visual process, known as hyperacuity, allows perception of an object's positional accuracy well beyond visual acuity. Vernier acuity is the ability to detect misalignment in lines and objects, which can be an order of magnitude higher than visual acuity. Spatial aliasing associated with pixelation gives rise to jaggy diagonal lines, detected by vernier acuity before perception of pixelation in general. Reducing pixel size below visual acuity may not suppress all the effects of pixelation.<sup>3</sup>

### 1.2.3 Flicker

Fluctuations in display luminance give rise to an annoying flicker. Frame-by-frame writing of electronic displays requires sufficient frame rate to avoid flicker. The early movies picked up the name flicks due to inadequate frame rate. With increase of flicker frequency, flicker attenuates, approaching

## 6 INTRODUCTION

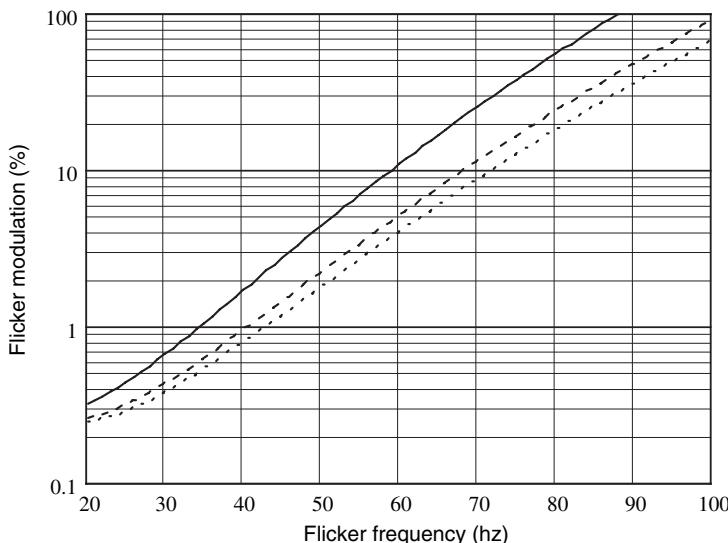

**Figure 1.6** Threshold modulation for 50% probability of seeing flicker on a full white screen. Average luminance: solid line  $100 \text{ cd/m}^2$ ; broken line  $500 \text{ cd/m}^2$ ; dotted line  $900 \text{ cd/m}^2$

threshold perception at a critical flicker frequency (CFF). Threshold perception is the level at which 50% of the population will detect flicker. Experimental studies of the dependence of flicker perception on luminance, modulation level, and frequency enable the elimination of display flicker.

The model for human vision referred to earlier generates Figure 1.6, on inserting typical parameters for threshold perception.<sup>2</sup> The flicker modulation  $m$  is of sinusoidal form  $[1 + m \cdot \cos(2\pi w t)]$ , at frequency  $w$  hertz. For non-sinusoidal flicker,  $m$  is the value of the fundamental Fourier component. The flicker parameters generating Figure 1.6 assume the worst case of a completely white screen at full brightness, a severe test of flicker compared with typical video projection. Perceptible flicker modulation decreases with increase of luminance, demanding a higher flicker frequency for suppression. An adjustment of the model parameters will give plots for a lower probability of flicker perception, predicting display conditions to eliminate flicker for essentially the entire population.

### 1.2.4 Contrast Ratio

Contrast is an important characteristic of image quality; low-contrast images have a washed-out appearance. Contrast sensitivity plots such as Figure 1.5 show that high contrast is required to achieve limiting eye resolution. High contrast ratio in all primary color channels promotes strong color saturation, and eliminates low-level color distortion, e.g. true black rather than dark purple.

The eye adapts to changes in average luminance, enhancing the visibility of dark scenes in a movie. To maintain image quality in dark scenes requires adequate contrast ratio at low luminance, implying high contrast at full luminance. Cinema-quality imaging requires  $\text{CR} > 1000$  to reveal detail in dark scenes.

Ambient light reflecting from the display surface sets a minimum luminance level, requiring higher display luminance for a given CR. Screen luminance  $< 60 \text{ cd/m}^2$  is accommodated by low lighting in a cinema supporting  $\text{CR} > 1000$ . Monitor displays designed for typical office lighting favor luminance of  $150 \text{ cd/m}^2$  or higher, and light reflected from the screen may degrade  $\text{CR} < 50$ . Outdoor displays exposed to sunlight demand extreme luminance, prompting the development of reflective displays that

exploit the high luminance environment. Shielded viewing inherent to NTE displays makes them insensitive to ambient light.

### 1.2.5 Grayscale

Analog displays such as CRT and LCD are continuously variable, making grayscale accuracy an issue of stability and noise. The advantages of digital systems result in a digital video signal converted to analog form to drive an analog display. Digital look-up tables (LUTs) assure the correct analog drive level, but digital bit-depth limits the number of gray levels. Making any display part of a digital system imposes grayscale quantization. Displays with only on/off luminance capability are inherently digital and achieve grayscale by pulse width modulation (PWM), averaging to the desired gray level over a frame period. Binary pulse code modulation generates equally spaced luminance levels over the luminance range; a poor match to the eye with an approximately logarithmic response to luminance, requiring progressively increasing steps in luminance for a perceptually uniform grayscale.

An inadequate number of gray levels gives rise to a contouring artifact in regions of near uniform luminance (e.g. image of sky), where the minimum quantized step is visible as an edge depicting the luminance contour.<sup>4</sup> A similar effect in color quantization appears as color contour boundaries, described as posterizing. At a given light level, fewer than 100 gray levels are required to avoid luminance contouring, provided the gray level steps are perceptually uniform, i.e. logarithmic. To provide adequate grayscale in dark scenes requires enhanced gray level count; cinema quality demands 1000 perceptually uniform gray levels.

Video image  $L_{\text{in}}$  transmitted with video signal voltage encoded  $V_s \propto L_{\text{in}}^{0.455}$ , to match typical receiving CRT luminance characteristic  $L_{\text{out}} \propto V_s^{2.64}$ , gives overall  $L_{\text{out}} \propto L_{\text{in}}^{1.2}$ . The display gamma ( $\gamma = 2.64$ ) is adjusted to the viewer's preference of image gamma. The image gamma determines the distribution of grey levels in an image, where adjustment of gamma allows the viewer to optimize the appearance according to taste and viewing conditions. Video image gamma is typically set to 1.2, consistent with dimly lit viewing conditions; however, choice varies with image as well as individual.<sup>2</sup> It is interesting that fidelity in display engineering is usually overridden by viewer preference in choice of gamma. A similar distortion appears in choice of color temperature. Our vision evolved in response to daylight, making that the natural choice. However, given an adjustment in color temperature we will generally make color temperature higher than daylight, enhancing the blue region of the image spectrum.

### 1.2.6 Viewing Comfort

Adequate luminance and resolution are basic requirements for any display. The viewer's eyesight determines the upper limit on resolution. Tolerance to lower resolution depends on the information content of the display. The eye adapts to a wide range of luminance, making acceptable luminance dependent on ambient lighting and spurious display reflectance. Obviously, the display should be well engineered and in good working order, free from flicker and noticeable distortion. Direct-view displays should be set slightly below eye level, at a distance about two or three times the screen diagonal. Image quality is sensitive to viewing angle in some displays, and generally favors on-axis viewing.

Viewing comfort in head-mounted displays is much more sophisticated than in direct-view displays. Weight, size and balance have no counterpart in direct view, but are critical to HMD tolerance. Total-emersion HMDs concentrate vision on the display, shutting out all extraneous light to provide an artificial reality experience. It is very difficult to simulate normal vision effectively over a realistic field of view, including eye and head movement. Inadequate simulation gives rise to motion sickness and other discomforts known collectively as simulator sickness.

Partial-emersion HMDs allow some vision of the outside world, which preserves the viewer's orientation, and are tolerable for much longer periods, even when the outside view is restricted to peripheral

## 8 INTRODUCTION

vision. Eliminating the influence of head movement on the displayed image makes eye movement do all the work in scanning the image. A field of view in excess of about 35 degrees induces intolerable eye fatigue due to the scanning effort. Viewing discomfort is a difficult barrier to overcome for the HMD to gain general acceptance. The interest in wearable computers and portable internet displays provides an incentive for further development and innovation in HMDs.

### 1.3 Display Specifications

A display designer emphasizes resolution, luminance, etc., according to the targeted application.<sup>5</sup> In marketing the display, a list of specifications identifies its value in various applications.

#### 1.3.1 Resolution and Size

Modulation transfer function (MTF) has the same functional form as Equation (1.1) for contrast, and describes the decline in contrast with spatial frequency in cycles/mm = (line pair)/mm = lp/mm. MTF is the standard method of describing the resolution of optical components such as a projection lens, and the product of component MTFs gives the overall MTF. Display resolution determined by raster scan or pixel count cannot be expressed in MTF form without loss of mathematical rigor. The number of TV lines or pixel array size characterizes display resolution. The video graphic adapter (VGA) notation, listed in Table 1.1, identifies standard pixel array formats, extended by inclusion of the high-definition television notation.

Screen diagonal characterizes the display size, a legacy of the early circular screen CRT. The cost of a direct-view display increases more rapidly than the area, since the defect probability and assembly problems increase. Plasma displays have demonstrated the largest diagonal in excess of 100 inches, followed closely by LCDs. The size and performance of flat panel displays competes with projection TV. When manufacturing costs have settled down, price will determine the target market for projection, now set at >40 inches diagonal. TV displays viewed at a distance two or three times the screen diameter barely resolve (1 arc min acuity) pixels at WXGA resolution, while computer monitors viewed at a distance comparable to screen diameter just resolve WUXGA. Higher visual acuity of lines and edges favors extended display resolution. HDTV at 1080 × 1920 resolution may pull the viewer closer to the screen, intensifying the experience, particularly for sporting events.

#### 1.3.2 Luminance and Color Saturation

In CRT projectors and plasma flat panels, the peak luminance cannot be maintained over the entire screen due to limited power dissipation. A peak luminance and an average luminance should be specified. Consumer CRT projectors deliver an average of about 200 lumens to the screen and require high screen gain for adequate luminance of about 350 cd/m<sup>2</sup>. Projectors in general can take advantage of screen gain to increase the screen luminance in a preferred direction at the expense of lower luminance in other directions. The focusing and scattering properties designed into the screen determine its gain.

**Table 1.1** Video graphic adapter designation and array size

|      |             |            |             |              |             |

|------|-------------|------------|-------------|--------------|-------------|

| VGA  | 640 × 480   | SVGA       | 800 × 600   | XGA          | 1024 × 768  |

| SXGA | 1280 × 1024 | UXGA       | 1600 × 1200 | QVGA         | 320 × 240   |

| WXGA | 1365 × 768  | WUXGA      | 1920 × 1200 | GXGA         | 2560 × 2048 |

| SDTV | 729 × 480   | HDTV(720P) | 1280 × 720  | SHDTV(1080P) | 1920 × 1080 |

Increased screen gain has the downside of enhanced speckle as well as reduced viewing angle. Front projectors specify lumens delivered to the screen, since the luminance depends on screen area and gain. Rear-projection units have built-in screens and luminance quoted over a range of viewing directions. Acceptable luminance depends on ambient lighting. Cinema projectors illuminate a large area screen to give about  $60\text{ cd/m}^2$  screen luminance, and require a dark ambient environment to appreciate image quality. Microdisplay projectors aim for  $500\text{ cd/m}^2$  or higher to accommodate the higher ambient light favored by the business and consumer markets.

Color saturation is strongest in laser or LED driven displays, with sharply defined wavelength. Dichroic filters in arc-lamp projection displays determine the color, where stronger color saturation implies lower throughput lumens. Specification of projector output luminance is sometimes inflated by quoting the value obtained before color correction. A similar tradeoff applies to LCDs using dyed pixels for color, where optical absorption introduces severe throughput loss. Phosphor characteristics limit the color saturation of plasma and CRT displays; however, color saturation is sometimes enhanced by addition of dichroic filtering in CRT projectors.

Backlighting power and throughput efficiency determine the luminance of LCDs. Improvements in throughput efficiency should improve the already high luminance of  $500\text{ cd/m}^2$ . Plasma displays are marketed with small-area luminance beyond  $500\text{ cd/m}^2$ . Microdisplays reduce cost by shrinking the diagonal to 0.7 inches or less. The development of small-arc projection lamps has kept pace with microdisplay contraction, maintaining the optical collimation necessary for efficient lumen throughput. We are entering an intense stage of competition for large-screen home theatre, where several technologies vie for consumer attention.

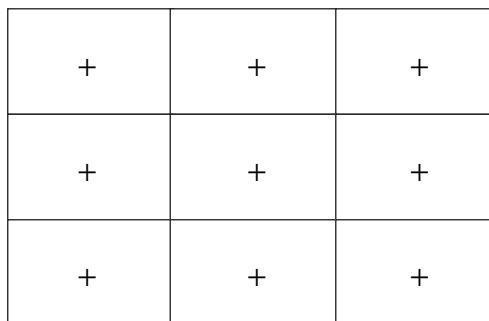

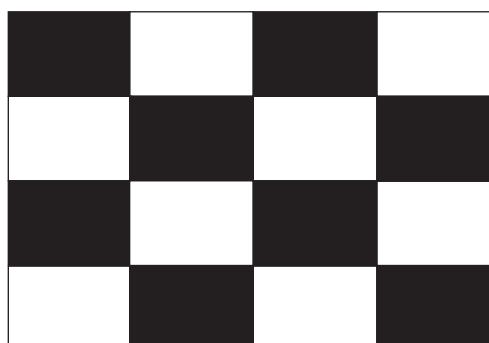

### 1.3.3 Contrast Ratio and Grayscale

Contrast ratio is an important indication of image quality. It is quoted for dark ambient; room lighting always reduces the CR. The largest degradation in CR is associated with diffuse reflecting surfaces, such as the powder phosphors in CRTs and plasma displays. Projectors quote the serial all-on/all-off CR, along with the ANSI CR for a white/black checkerboard pattern; ANSI CR is always lower than the serial CR, due to internal light scattering, and provides a better indication of image quality. LCD CR is limited by the extinction ratio of polarizing optics and off-axis retardation dependence; however, optical compensation achieves  $\text{CR} > 500$ . Projection systems achieve  $\text{CR} > 1000$ , due to higher quality polarization optics and better compensation over the limited field angle of the projection lens. A recent development expands the effective CR by modulating the light source according to the image's average light level, to maintain excellent CR and grayscale in dark scenes.<sup>6</sup>

The standard 8-bit grayscale is adequate for most purposes, and applied to each primary color channel gives 24-bit color. More demanding applications such as cinema projection require 12-bit grayscale/channel. Look-up tables create appropriate luminance grayscale steps, taking into account the device characteristic. Pulse width modulation grayscale, necessary in plasma displays and other digital display devices, achieves high precision in grayscale; however, image contouring and motion artifacts associated with PWM requires an effective expansion in addressing bit depth.

### 1.3.4 Response Speed and Flicker

Video displays need to respond at a fast enough rate to avoid motional blurring and flicker. We are somewhat forgiving of motion blur, since our vision is less acute in observing movement. Movies shot at 24 frames/sec are acceptable, which is not very challenging for an electronic display response time. However, cinematographers structure the scenes and camera angles to minimize artifacts such as false wheel rotation; a higher frame rate is desirable. Theatres shutter the film projector to raise the flicker rate to 48Hz or higher to suppress flicker perception. Motion picture frame time is 42 ms, but the frame changes abruptly,

## 10 INTRODUCTION

implying equivalent display response  $\ll 42$  ms to duplicate film. A video data rate of 60 frames/sec attenuates flicker, but requires response  $\ll 17$  ms to maintain gray level integrity and avoid trailing on fast-moving images. The response time is severely challenged in color field sequential displays, where color is formed by a rapid succession of primary color frames above the color fusion frequency of the eye. Color frame rates as high as 540 frames/sec are required to avoid color breakup caused by eye movement.

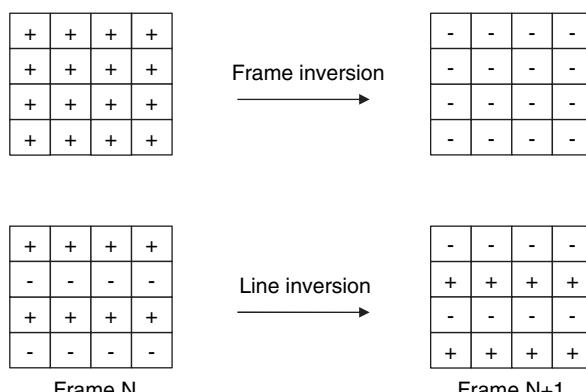

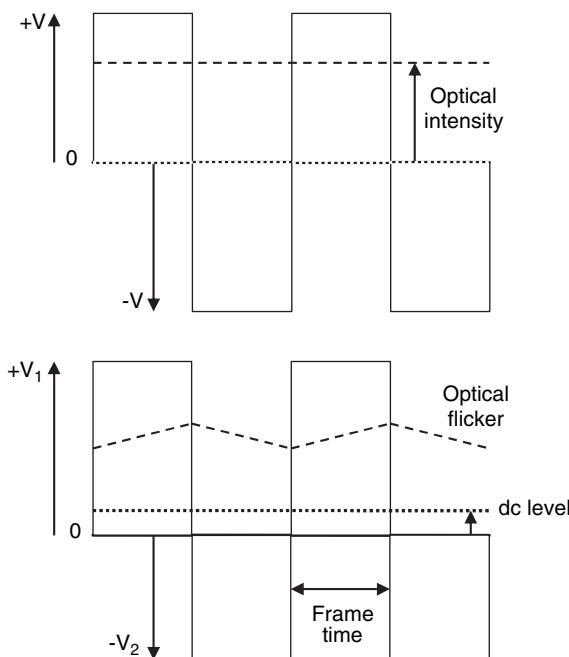

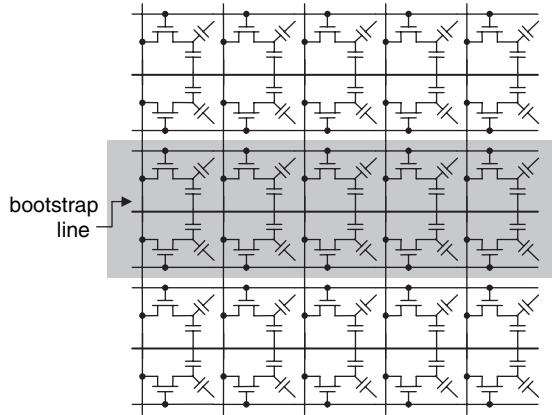

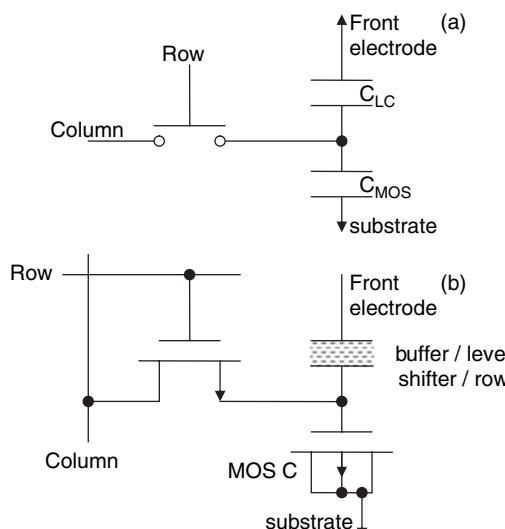

The image refresh rate introduces an intensity modulation at the refresh frequency, and half that frequency if the display mechanism is susceptible to odd/even asymmetry as in the LCD. Flicker issues are resolved in display design by minimizing the flicker modulation and raising the refresh frequency. The displayed frame rate may be doubled to reduce flicker if there is significant modulation at half frame rate.

A static image displayed for a substantial period may store some aspects of the image that persists for some time as a 'ghost image' superimposed on the newly addressed image. The effect is described as ghosting or image sticking. Liquid crystal displays are susceptible to image sticking due to ionic charging effects. Plasma displays are also prone to ghost image effects.

### 1.4 Displays in General

To place microdisplays and applications in context we discuss electronic displays in general and the shrinkage of direct-view displays into the micro domain. We restrict our attention to high-information-content displays, since there is little value in magnifying low information content capable of direct display.

#### 1.4.1 Cathode Ray Tube

The CRT has been the dominant technology for many years. Reliability and low cost have outweighed its shortcomings, until recent developments in flat panels. The simplicity of electron-beam addressing remains appealing, but carries vacuum-tube baggage that occupies valuable space, and has become unfashionable. The shape of the tube has improved over the years, including attempts at a flat structure, but does not compare with a lightweight flat panel display. The tradeoff in luminance versus resolution is a technical limitation that is proving difficult to surmount. Diffuse reflection from the phosphor powder penalizes CR under modest room light. The direct-view CRT will play a prominent role in displays for many years and gradual improvement in performance will continue. However, flat panel performance is improving more rapidly and will continue to win market share from CRTs.

The luminance/resolution issue is more marked in projection CRTs, where inadequate luminance is the biggest drawback. Improved phosphors and the application of thin film phosphors should enhance performance. However, competitive pricing of high-quality microdisplay rear-projection HDTV is pushing the CRT units off the showroom floor. The development of large-area flat panel displays competes with projectors in general.

Miniature CRTs were developed for NTE displays such as military helmet displays. As microdisplays, they played an important role in the development of head-mounted displays, and are still in use. Microdisplays with superior performance and advantages in weight and volume have made the miniature CRT obsolete. Detailed discussion of microdisplays in later chapters excludes CRTs, because they do not provide much insight into current microdisplay development.

#### 1.4.2 Matrix Addressed Displays

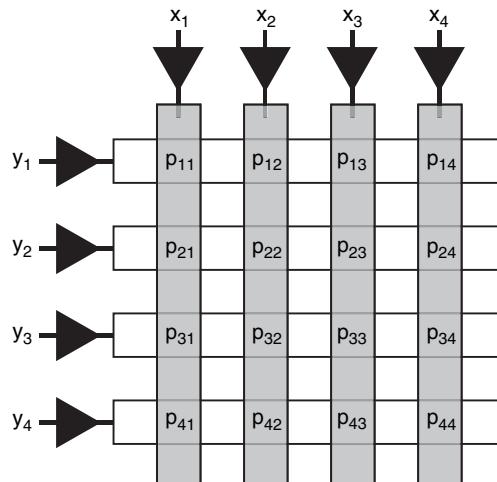

Electrode-addressed displays, such as liquid crystal displays, must use multiplex addressing to reduce the wiring complexity. Matrix addressing uses a rectangular network of electrodes similar to  $(x,y)$

Cartesian coordinates, to address a pixel located at the  $(x,y)$  intersection of the electrodes. A rectangular array of  $M \times N$  pixels can be addressed by  $(N + M)$  electrode lines, plus the common return line. Detailed analysis of matrix addressing shows that the electro-optic response of the pixel must be highly nonlinear to address a large number of pixels in an independent manner. Moreover, line-by-line addressing implies average luminance decreases with increase in addressed lines, unless the pixel is bistable. Devices such as plasma displays have nonlinearity favoring high-resolution addressing and bistability, accounting for their early success as flat panels.

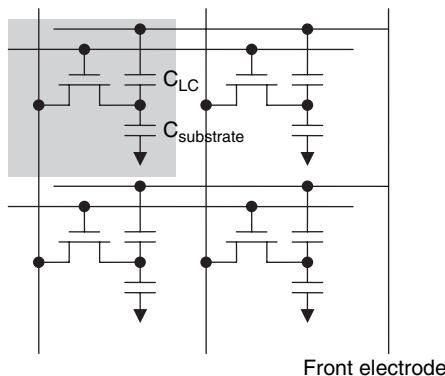

Early LCDs adopted cell designs that optimized the performance for passive matrix addressing, at the expense of response speed and CR. Active matrix addressing developed to eliminate the need for nonlinearity in the electro-optic response. A field effect transistor at each pixel activates the pixel according to the  $(x,y)$  addressing signal, and isolates the pixel between refresh cycles. The development of amorphous-silicon ( $\alpha$ -Si) thin film transistor (TFT) arrays enabled large-area active-matrix liquid crystal displays (AMLCDs), with nematic liquid crystal (NLC) cell design optimized for display performance.

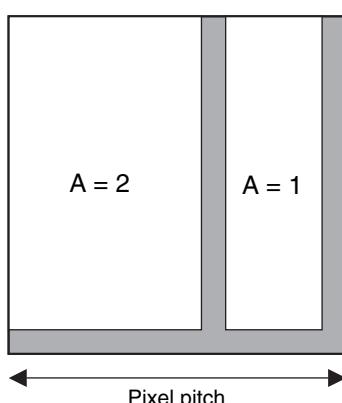

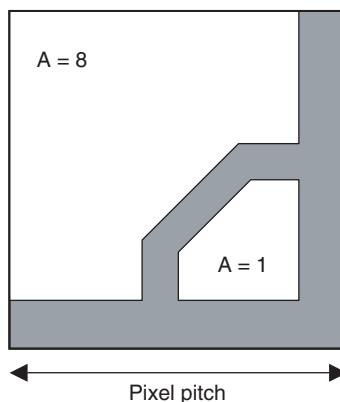

A large-area display has plenty of peripheral space to make connection to the matrix electrodes, or accommodate chip-on-glass methods to reduce the external connections. However, the small electrode pitch ( $\sim 10\mu\text{m}$ ) of a microdisplay discourages external connections and peripheral space is minimal. The best solution is to incorporate the addressing electronics with the electrode matrix.  $\alpha$ -Si transistors are inadequate for the addressing electronics, where polysilicon or single-crystal silicon (c-Si) devices are favored. High-temperature polysilicon circuitry on quartz provided the first AMLCD microdisplays used in projectors. Silicon wafer technology is cost-effective in microdisplays, but favors reflective rather than transmission optics, e.g. the liquid-crystal-on-silicon (LCOS) microdisplay.

### 1.4.3 Field Emission Displays

Field emission displays (FEDs) employ cathodoluminescence similar to the CRT, but the electrons are field-emitted from multiple cathodes, rather than thermo-emitted. A vacuum tube environment is still required, but multiple cathodes support a flat panel structure. Each source pixel contains many cathodes, with emission modulated by control gates, and focused to activate a similar sized phosphor pixel. The pixels are matrix addressed by driving the voltage between control gates and cathodes. A revival of interest in FEDs is making slow progress in competing with established flat panel displays, and rapid advances in OLEDs. Early development of an FED microdisplay yielded little published data, and transformed into a successful OLED program. FED remains an interesting technology, but is unlikely to compete in the microdisplay arena. In keeping with miniature CRTs, the need for a high-voltage and vacuum environment is an overwhelming handicap in NTE applications.

### 1.4.4 Plasma Displays

Light emitted from a gas discharge, similar to neon lighting, is the basis of plasma display panels (PDPs). Designing the gas discharges to emit UV light that excites primary-color phosphors provides a full-color display. The outstanding feature of the PDP is large screen area, with diagonal beyond 100 inches, and still growing. It provides peak luminance greater than  $500\text{cd}/\text{m}^2$ , and high  $\text{CR} > 1000$  in a dark ambient. In ordinary room light, the CR may drop considerably due to optical scattering from the phosphors and plasma screening filter. Pulse width modulated grayscale and susceptibility to image burn-in are handicaps. The PDP competes in the business and consumer home-theater markets. The structural complexity to address and control the discharge has prevented the plasma display from shrinking to microdisplay dimensions.

## 12 INTRODUCTION

### 1.4.5 Liquid Crystal Displays

Displays utilize the birefringence property of liquid crystals to modulate polarized light, or create strong optical scattering. High-resolution video displays favor polarization modulation, requiring the additional complication of polarizing optics. There are a number of nematic liquid crystal (NLC) cell configurations, such as twisted nematic (TN), and vertical aligned nematic (VAN), each having some advantage in a given application. A large electro-optic effect at a low voltage is the overwhelming advantage of liquid crystals, together with video response speed.

Liquid crystals modulate light, enabling operation in sunlight using a reflective configuration. Back-lighting gives the best performance in ordinary room light, and pixel dyes provide primary color pixels to form full-color images. Pixel dye losses sacrifice optical throughput efficiency, which would benefit from improved color filtration methods. The gray levels are dependent on viewing angle, but various compensation schemes have evolved to minimize the off-axis image degradation. AMLCD covers a wide range of display sizes, from hand-held devices to large scale (>100-inch diagonal). Luminance  $>500\text{cd/m}^2$  is achieved, with CR  $> 500$ .

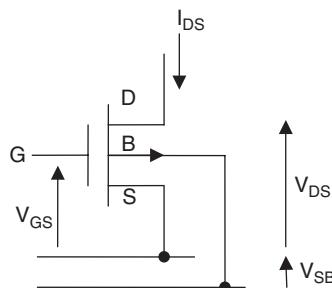

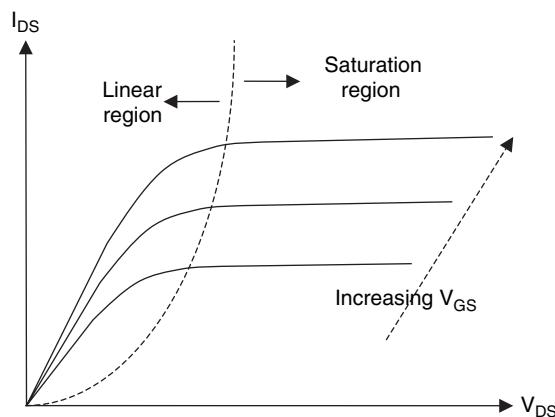

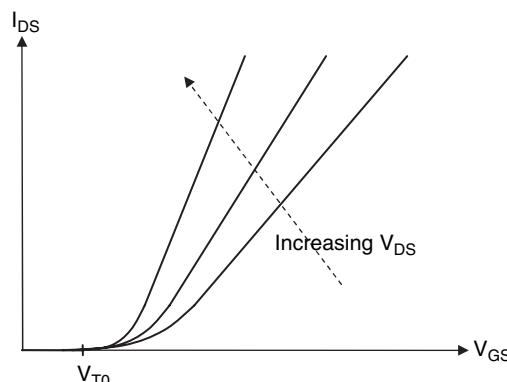

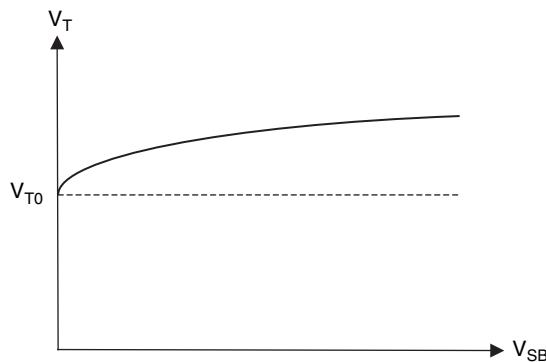

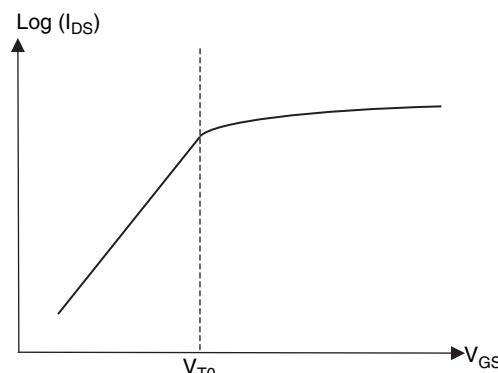

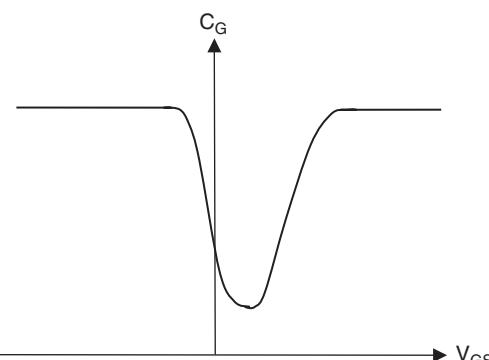

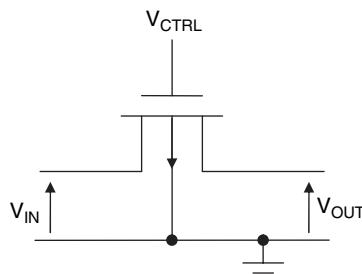

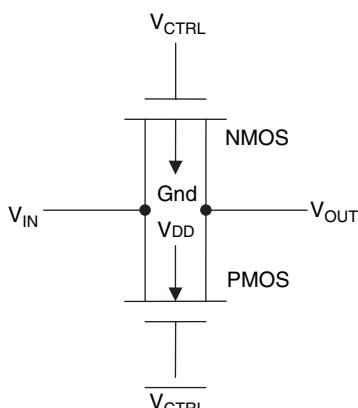

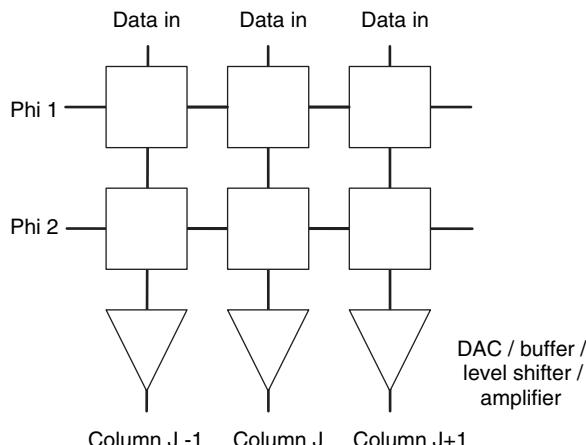

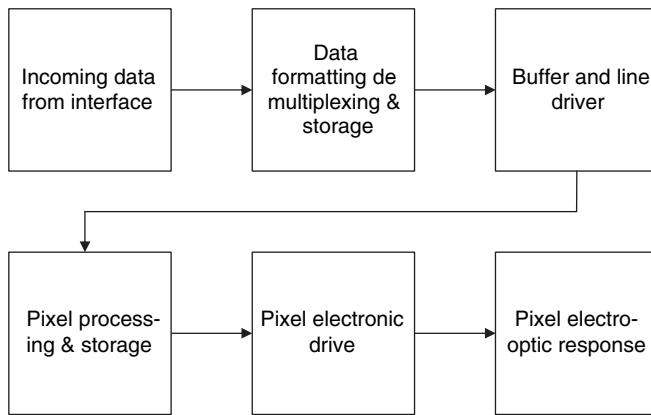

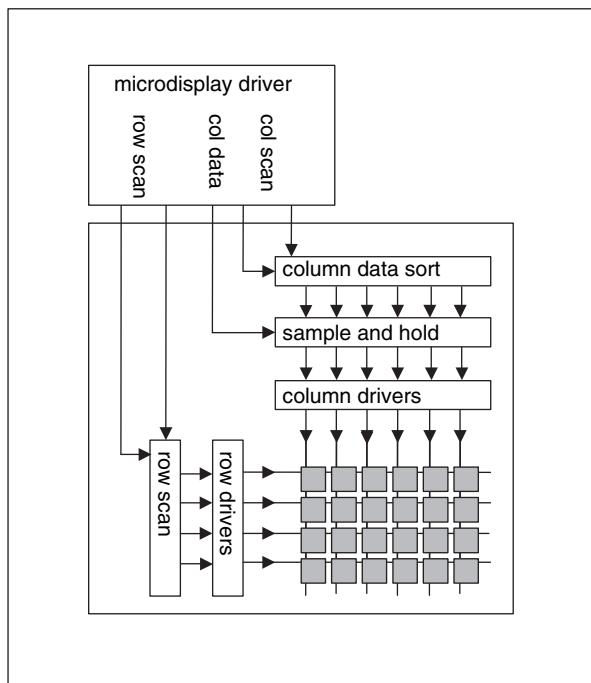

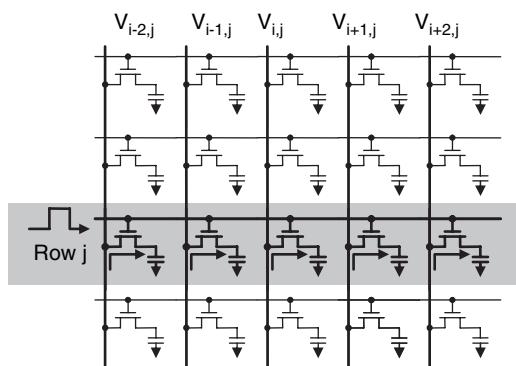

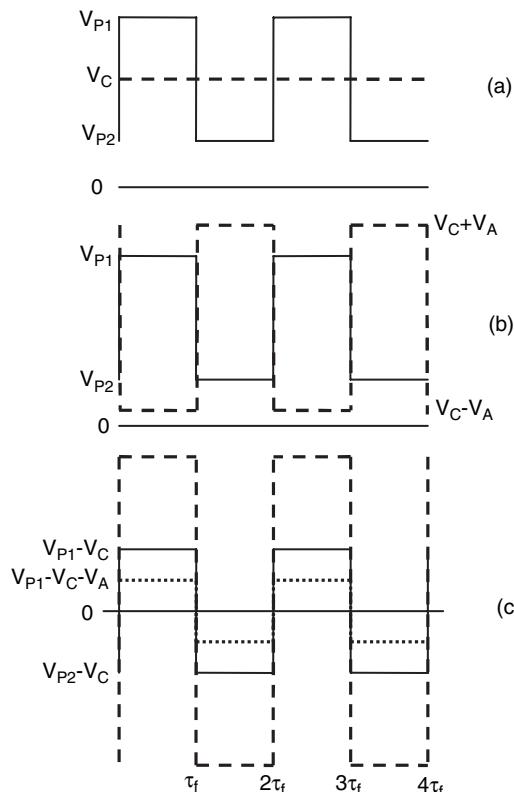

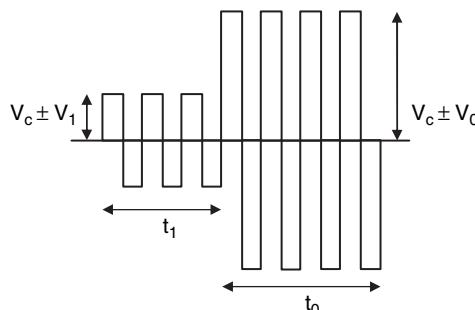

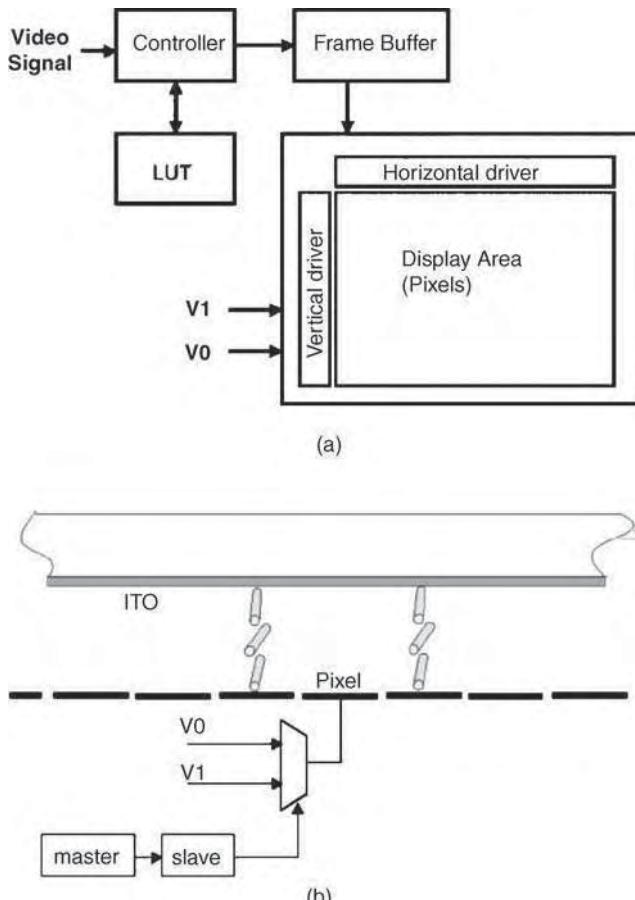

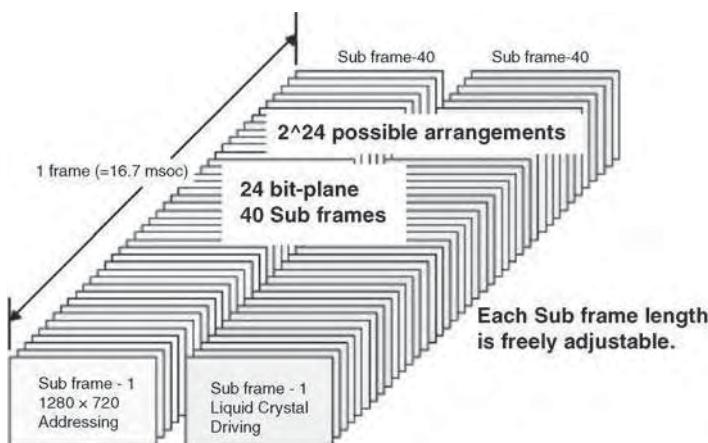

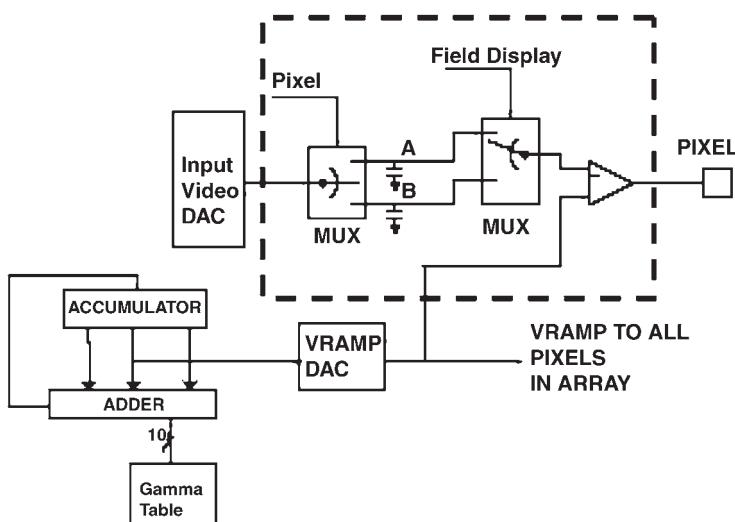

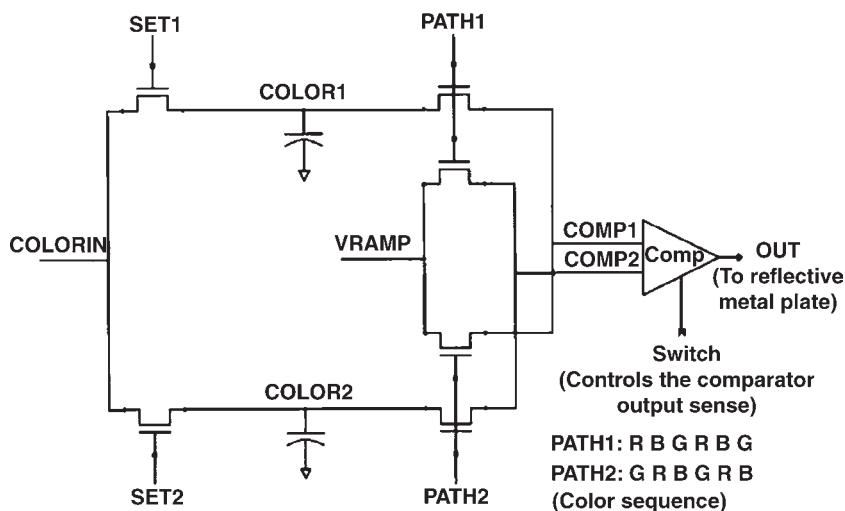

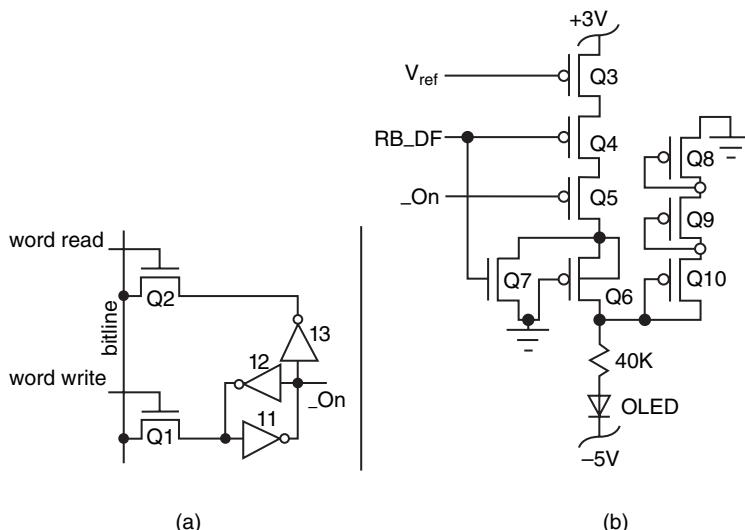

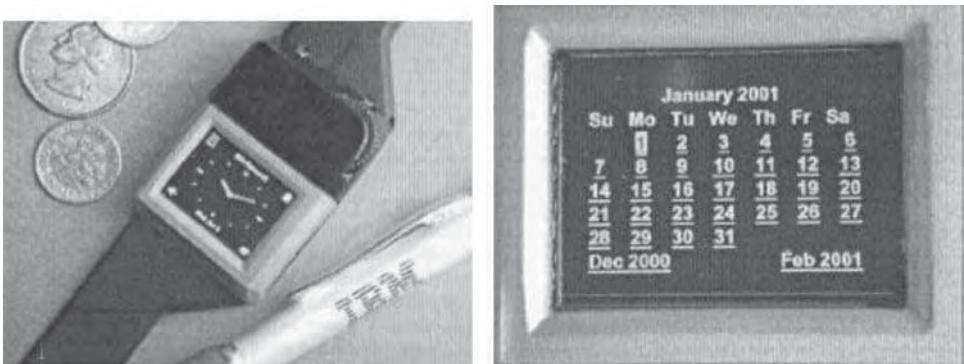

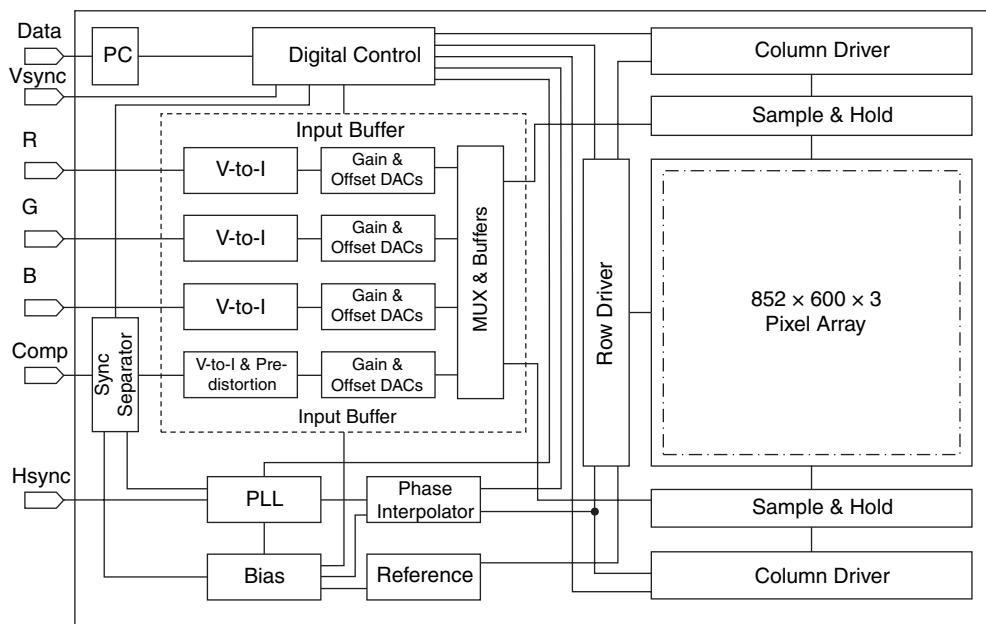

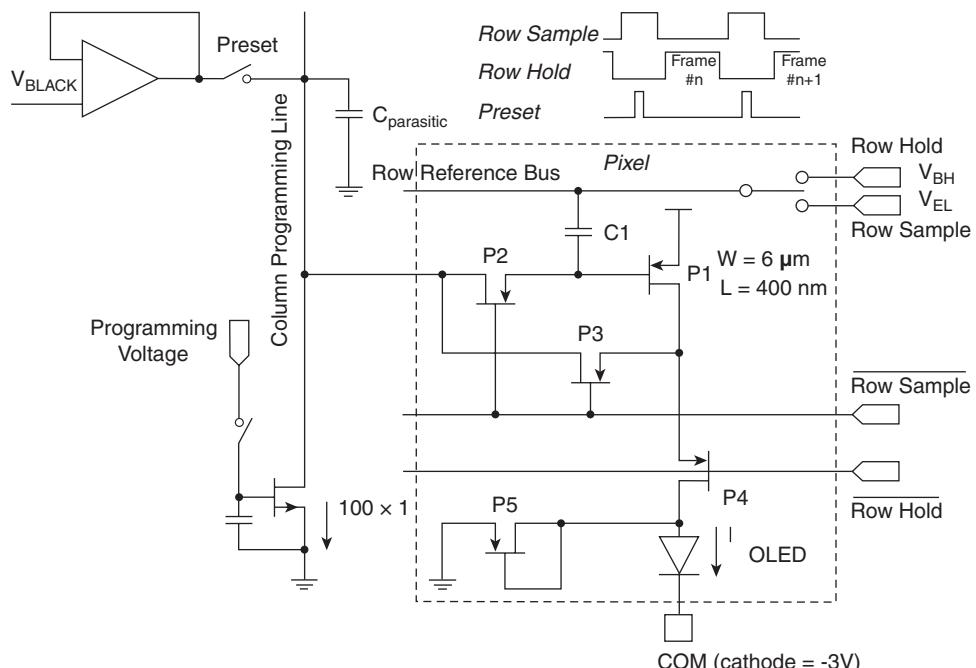

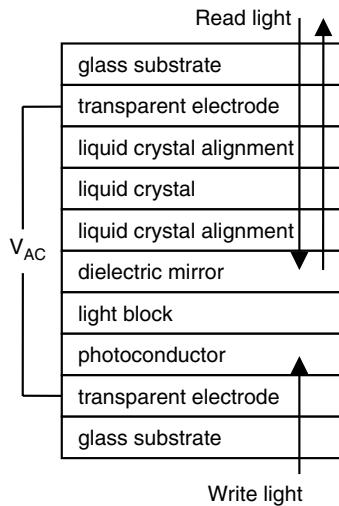

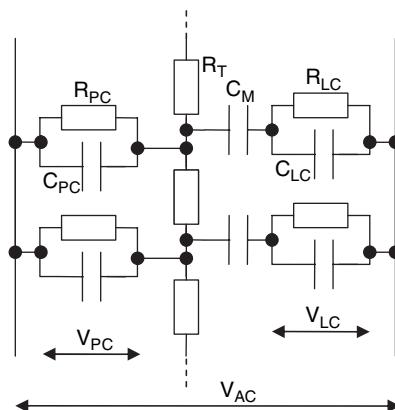

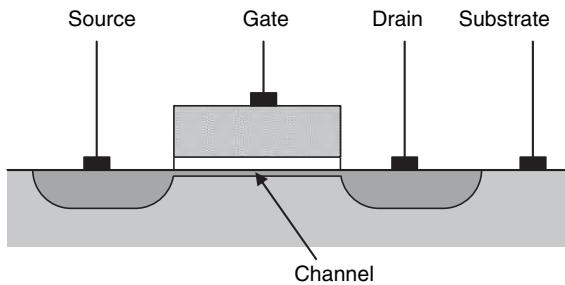

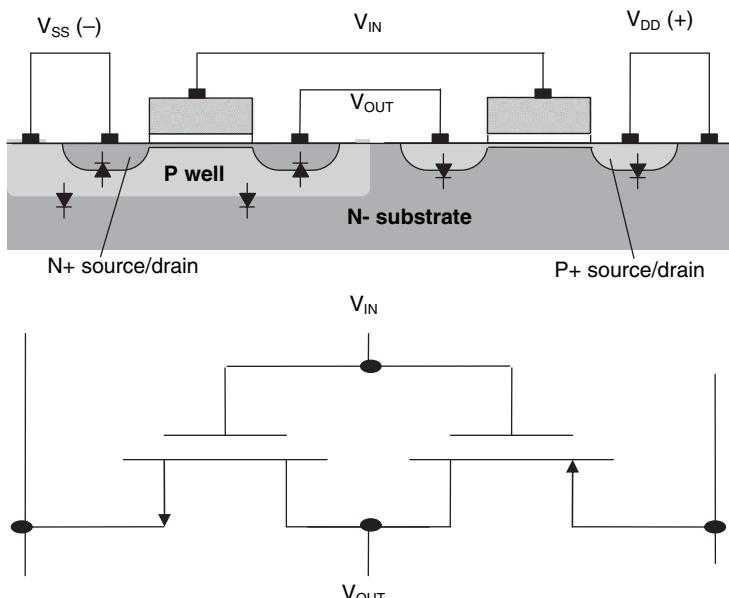

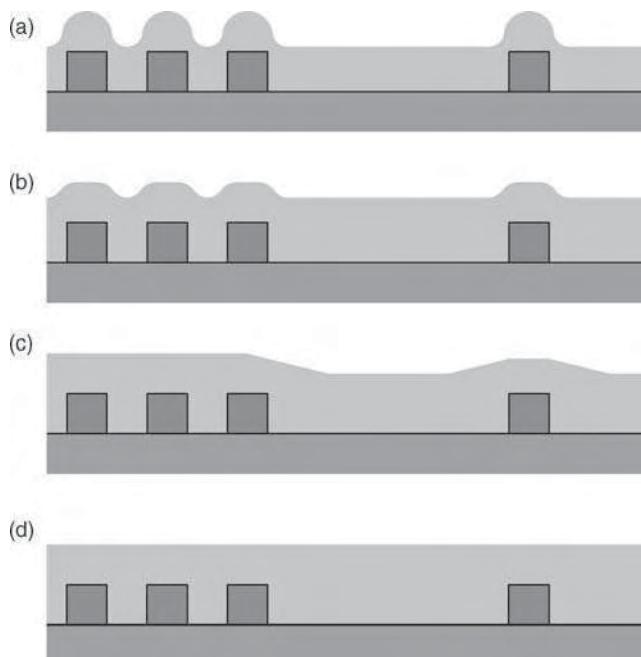

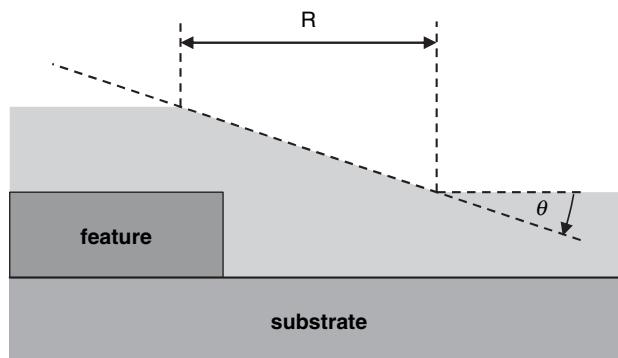

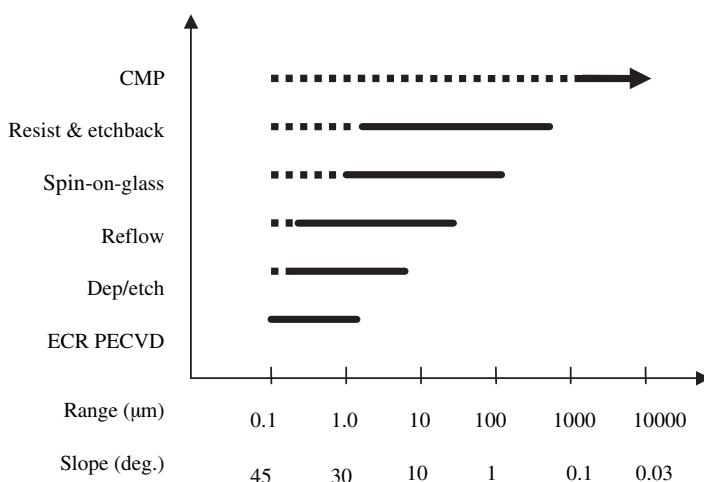

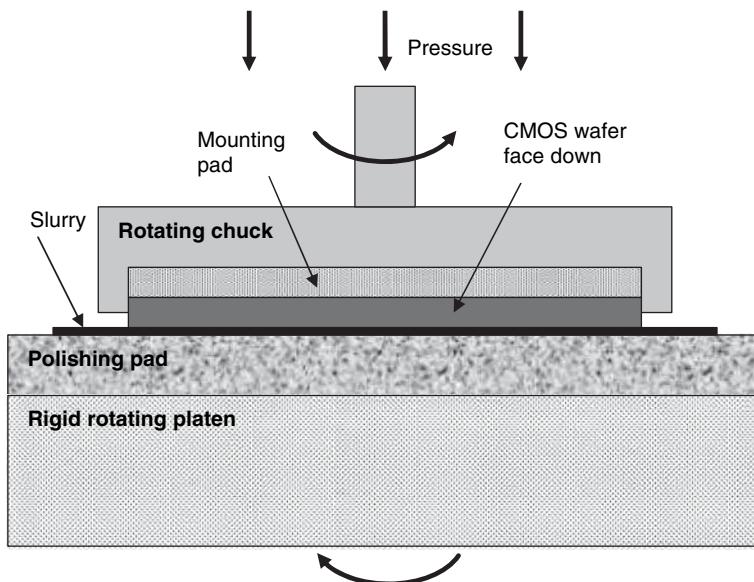

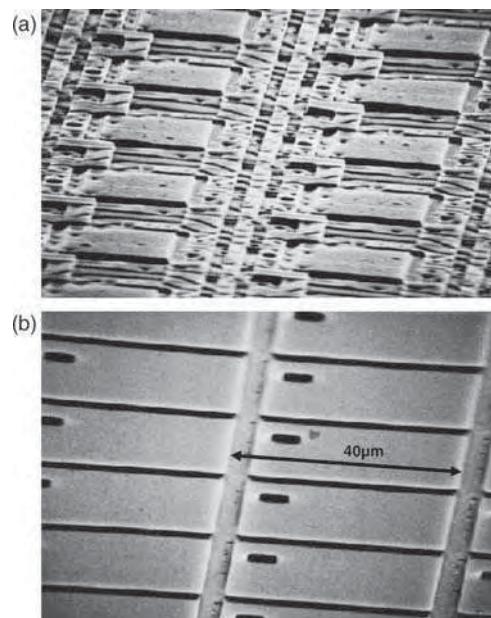

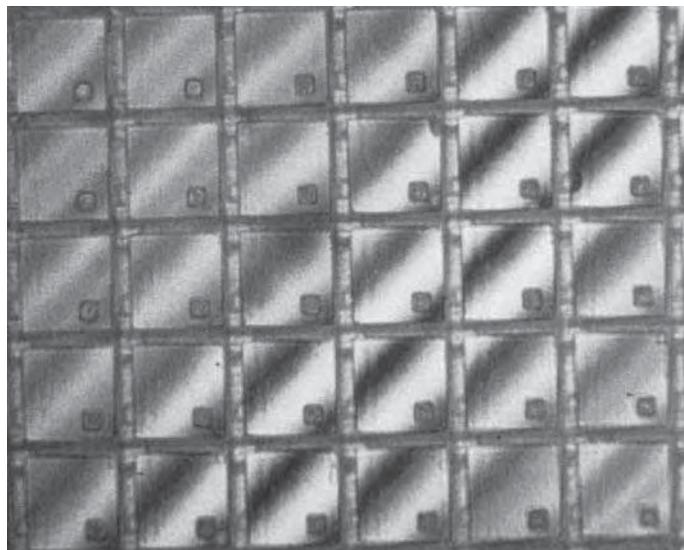

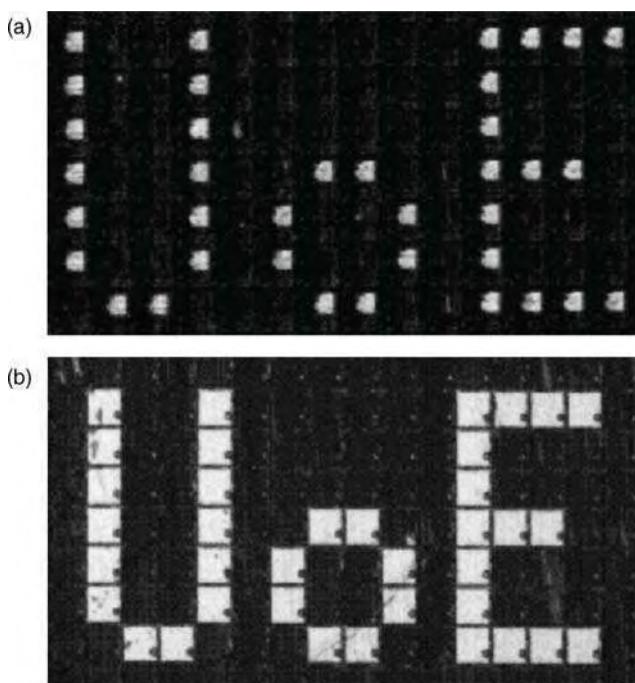

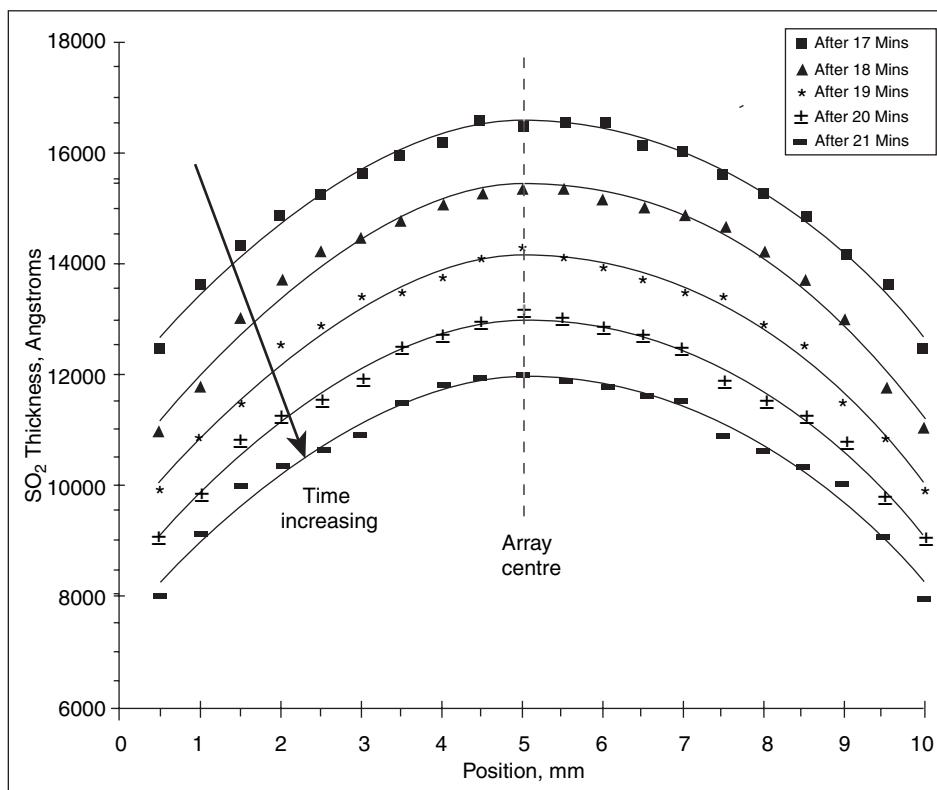

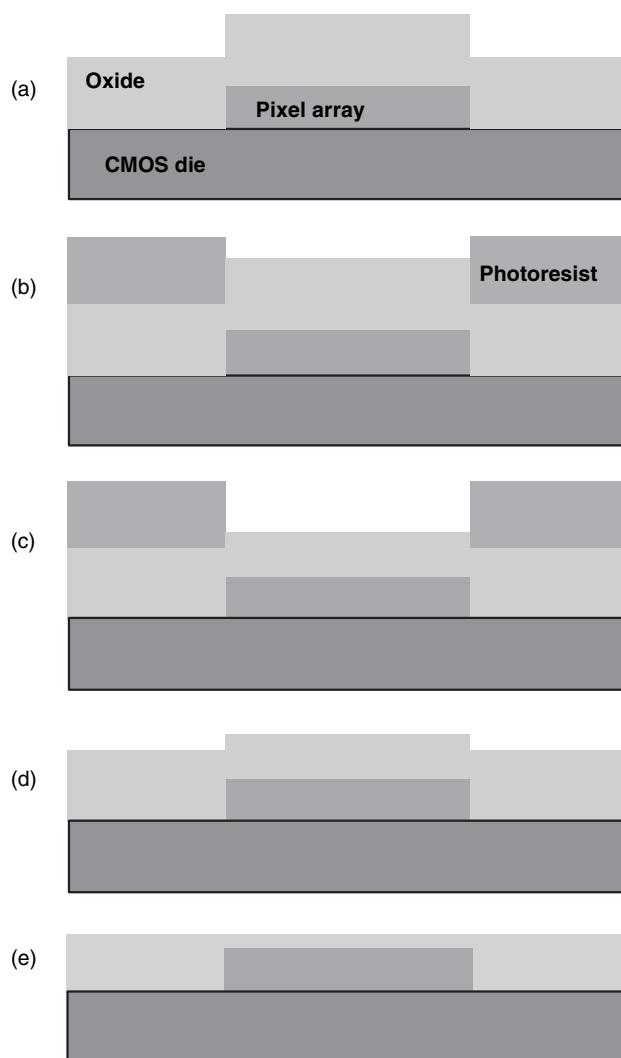

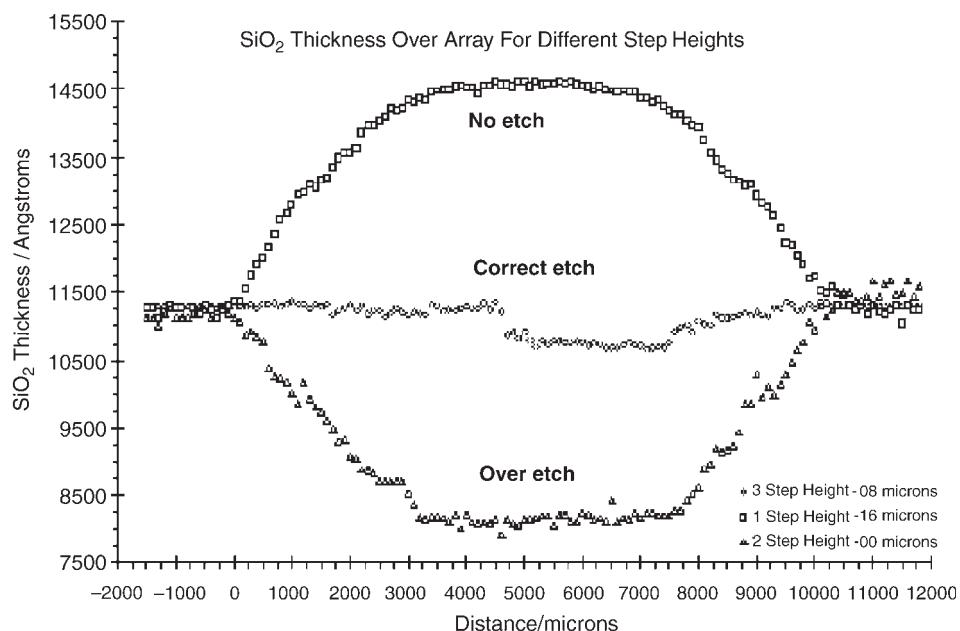

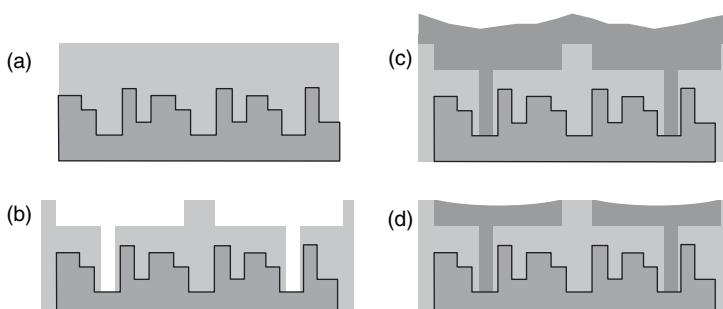

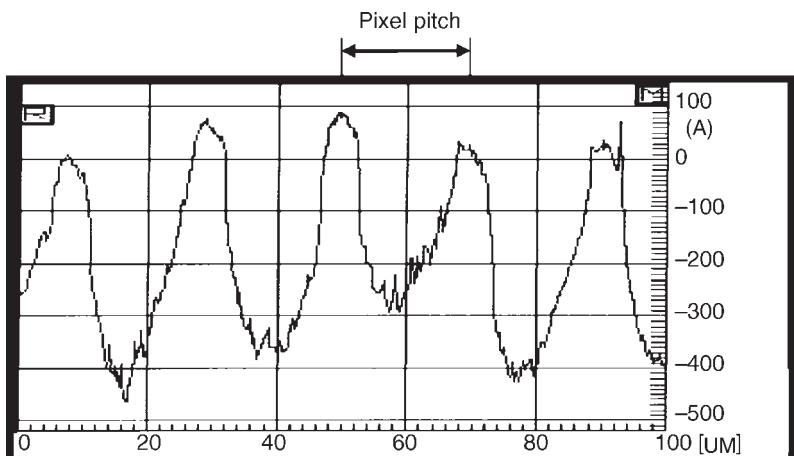

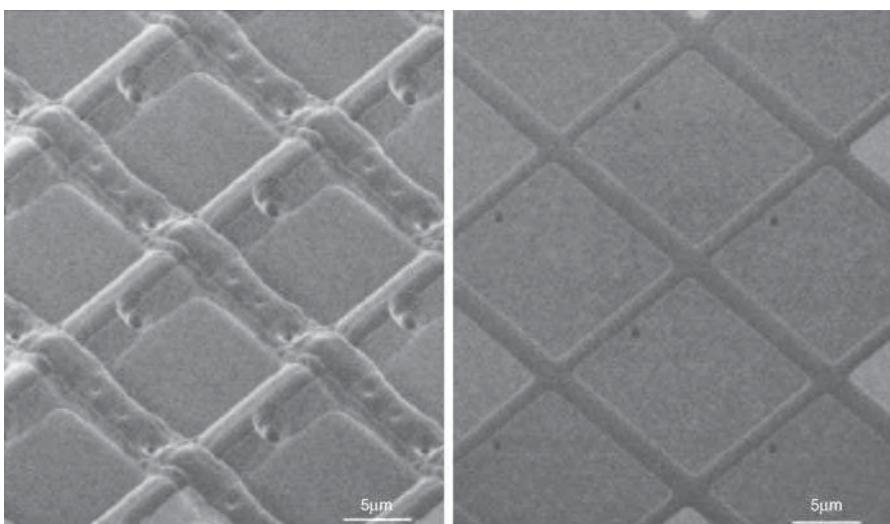

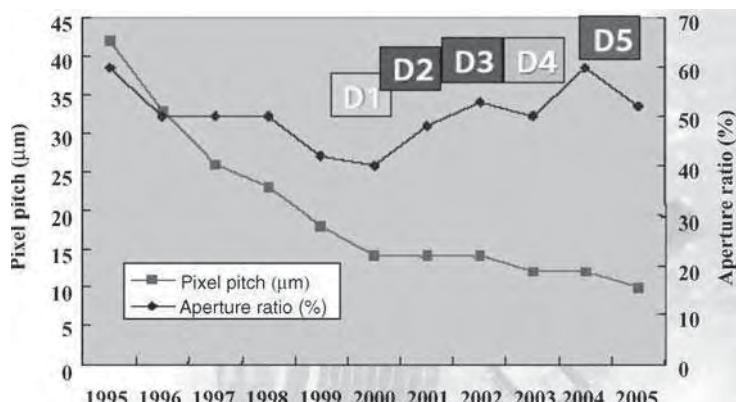

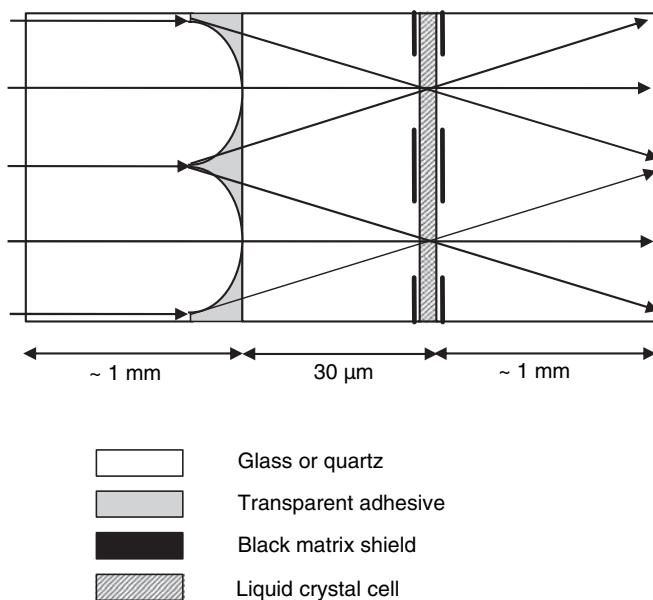

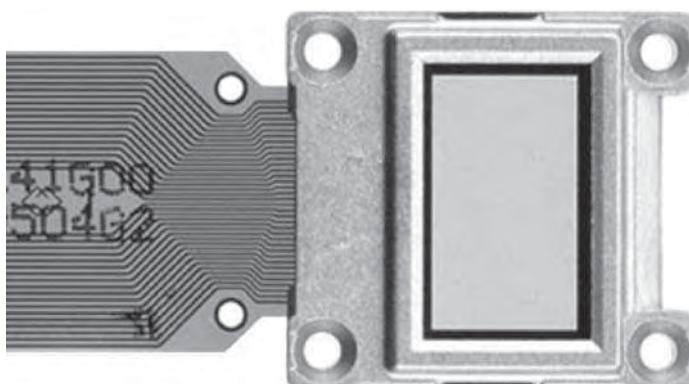

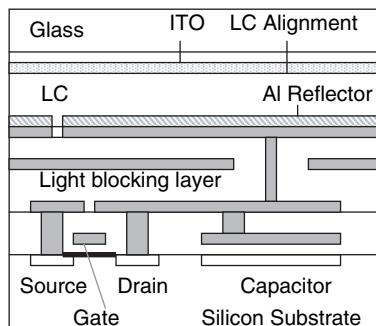

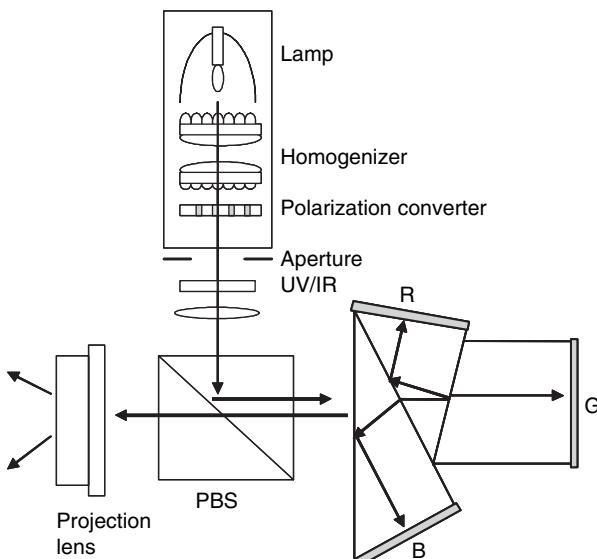

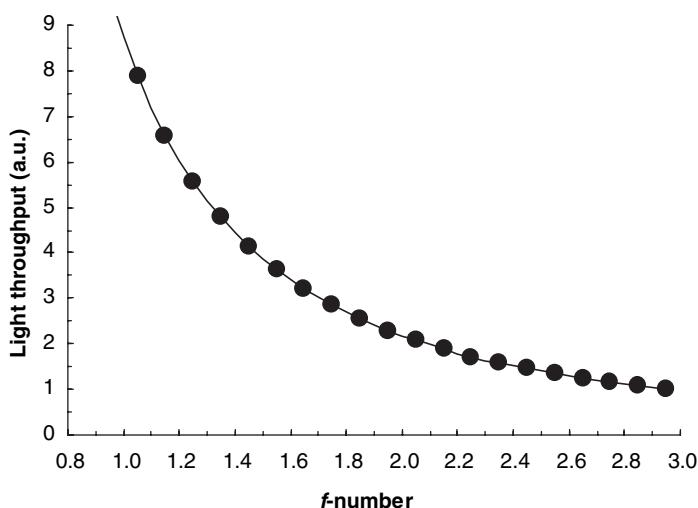

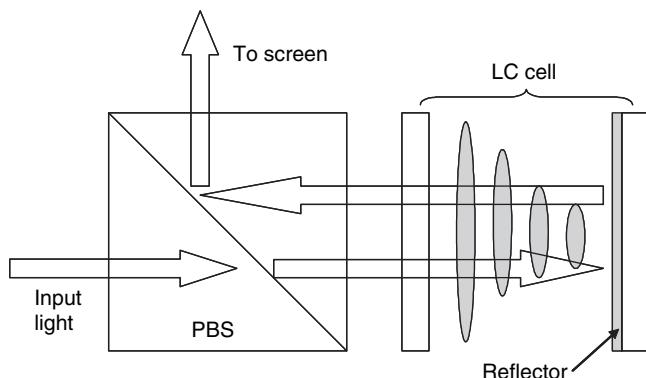

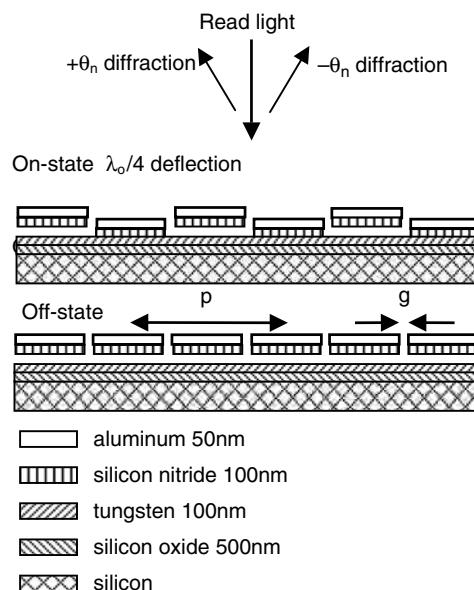

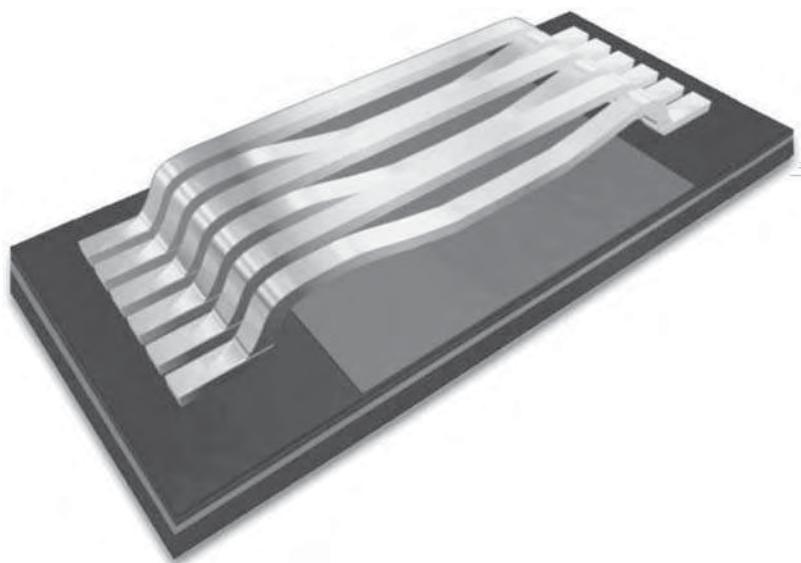

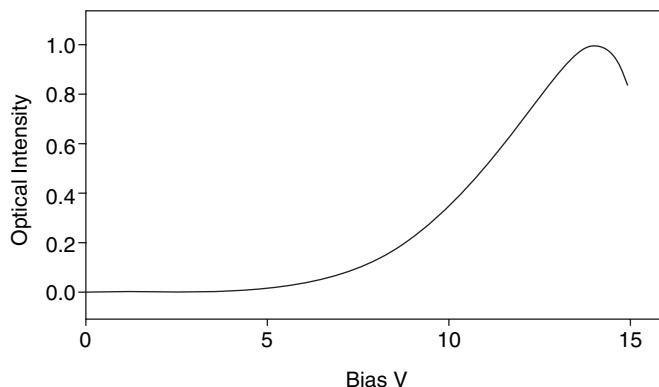

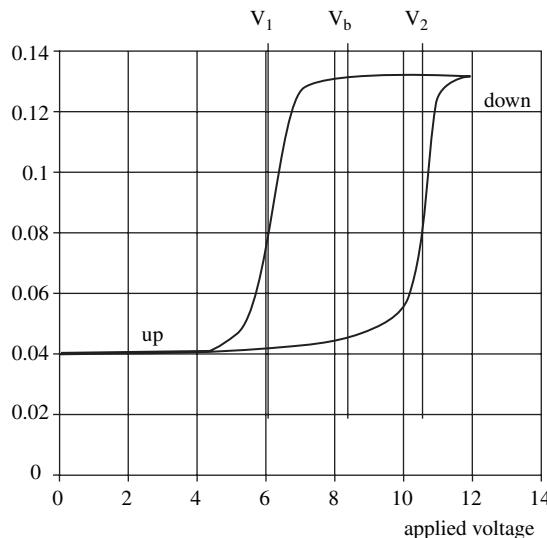

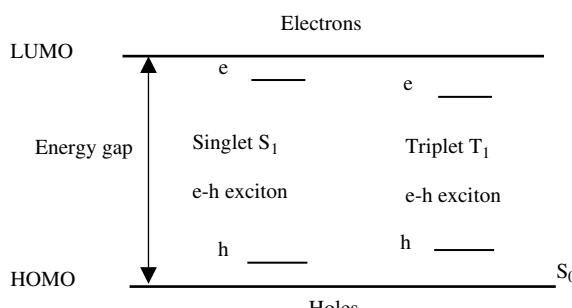

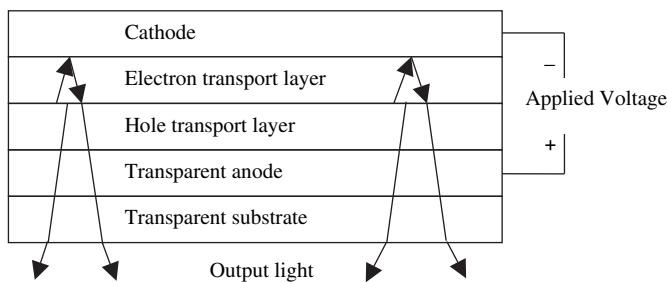

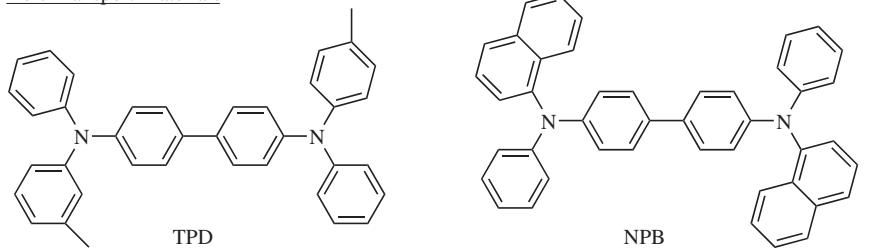

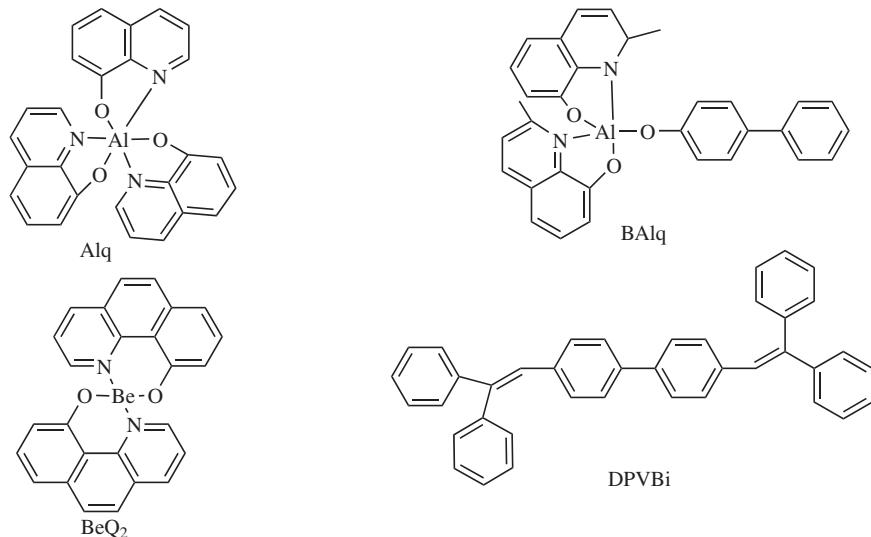

AMLCD adapts to microdisplay dimensions by incorporating the matrix addressing circuits on the matrix periphery. High-temperature polysilicon on quartz provides circuitry for AMLCD projectors and head-mounted displays. The application of silicon chip technology to fabricate LCOS microdisplays achieves pixel dimensions  $<10\mu\text{m}$ . LCOS promises lower-cost higher-performance projectors and NTE displays.